Для чего сумматоры имеют вход переноса с

Комбинационные микросхемы. Часть 2

Сумматоры

Сумматоры могут использоваться также для суммирования чисел в отрицательной логике (когда логической единице соответствует электрический нуль, и наоборот, логическому нулю соответствует электрическая единица ). Но в этом случае входной сигнал переноса С также становится инверсным, поэтому при использовании одной микросхемы сумматора на вход С надо подать электрическую единицу (высокий уровень напряжения). Инверсным становится и выходной сигнал переноса Р, низкий уровень напряжения на нем (электрический нуль) соответствует наличию переноса. То есть получается, что сумматор абсолютно одинаково работает как с положительной, так и с отрицательной логикой.

| Входы | Выходы | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| C=0 | C=1 | ||||||||

| A1 | A0 | B1 | B0 | P | S1 | S0 | P | S1 | S0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

Сумматор может вычислять не только сумму, но и разность входных кодов, то есть работать вычитателем. Для этого вычитаемое число надо просто поразрядно проинвертировать, а на вход переноса С подать единичный сигнал (рис. 6.2).

Например, пусть нам надо вычислить разность между числом 11 (1011) и числом 5 (0101). Инвертируем поразрядно число 5 и получаем 1010, то есть десятичное 10. Сумматор при суммировании 11 и 10 даст 21, то есть двоичное число 10101. Если сигнал С равен 1, то результат будет 10110. Отбрасываем старший разряд (выходной сигнал Р) и получаем разность 0110, то есть 6.

Еще пример. Пусть надо вычислить разность между числом 12 (1100) и числом 9 (1001). Инвертируем поразрядно 9, получаем 0110, то есть десятичное 6. Находим сумму 12 и 6, получаем 18, а с учетом С = 1 получаем 19, то есть двоичное 10011. В четырех младших разрядах имеем 0011, то есть десятичное 3.

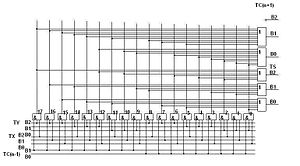

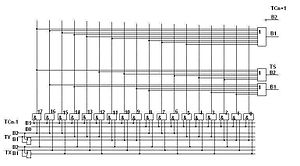

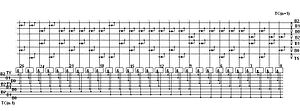

Неопределенные состояния на выходах сумматора могут возникать при любом изменении любого из входных кодов (рис. 6.4). Выходной код суммы может принимать в течение короткого времени значения, никак не связанные с входными кодами, а на выходе переноса могут появляться короткие паразитные импульсы. Это связано прежде всего с неодновременным изменением разрядов входных кодов. Чтобы избежать влияния этих неопределенных состояний на дальнейшую схему, необходимо предусматривать синхронизацию или стробирование выходных сигналов. Но для этого надо располагать информацией о моментах изменения входных кодов, которая имеется далеко не всегда.

Сумматоры: определения, классификация, уравнения, структуры и применение

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

Сумматоры классифицируют по различным признакам.

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединённых цепями переноса. Однако такая схема сумматора характеризуется сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом i-ом разряде производится лишь после того, как поступит сигнал переноса с (i-1)-го разряда.Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса. Уменьшение этого времени — основная задача при построении параллельных сумматоров.

Для уменьшения времени распространения сигнала переноса применяют: конструктивные решения, когда используют в цепи переноса наиболее быстродействующие элементы; тщательно выполняют монтаж без длинных проводников и паразитных ёмкостных составляющих нагрузки и (наиболее часто) структурные методы ускорения прохождения сигнала переноса.

Сумматоры, которые имеют постоянное время, отводимое для суммирования, независимое от значений слагаемых, называют синхронными.

Последние две структуры строятся либо на счётных триггерах (сейчас практически не используются), либо по структуре “комбинационный сумматор – регистр хранения” (сейчас наиболее употребляемая схема).

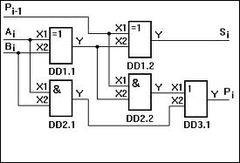

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент “сумма по модулю 2” и элемент “исключающее ИЛИ”. Схема (рис. 1) имеет два входа а и b для двух слагаемых и один выход S для суммы. Работу её отражает таблица истинности 1 (табл. 1), а соответствующее уравнение имеет вид

Что такое сумматоры?

Что такое сумматоры?