Dram write recovery time что это

SDRAM Write Recovery Time

BIOS-утилита SDRAM Write Recovery Time представляет собой функцию, регулирующую длительность задержки tWR оперативной памяти. Конфигурационные параметры: 1 Cycle, 2 Cycles, 3 Cycles.

Принцип работы

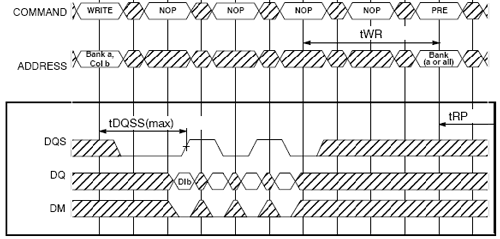

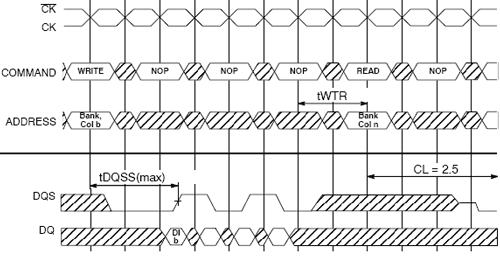

Данный тайминг расшифровывается как Write Recovery Time (Время восстановления при записи). Задержка tWR ― это временной интервал между окончанием операции записи в ячейку ОЗУ и началом ее регенерации. Эта задержка имеет особое значение, поскольку именно она гарантирует корректное завершение операции записи в память.

Чтобы не запутаться, нужно четко уяснить, что тайминг tWR не относится к процессу обновления ячейки и не определяет длительность цикла регенерации. Он управляет задержкой, которая предшествует обновлению банка памяти.

Понятно, что сокращение длительности любой задержки ускоряет процесс функционирования оперативной памяти. И данный тайминг не является исключением. Но не окажет ли эта мера отрицательного воздействия, к примеру, не приведет ли к потере данных или их повреждению? Именно так. Чем меньшее значение присваивается опции, то есть чем короче задержка tWR, тем выше вероятность того, что активный банк памяти не успеет завершить текущую операцию записи, и она будет прервана начавшимся циклом регенерации банка. Соответственно, использование излишне малой задержки приводит к повреждению записываемой информации и ее потере.

С другой стороны, небольшая задержка способствует повышению производительности ОЗУ, так как ее сокращенная длительность дает возможность ускоренного обновления банка для выполнения следующей операции.

Какое значение функции использовать?

Это зависит от модели ОЗУ, установленного в системе. Как правило, для модулей DDR200 и DDR266 оптимальная длительность задержки tWR составляет 2 цикла таймера. Соответственно, при наличии памяти именно этого вида следует установить для функции SDRAM Write Recovery Time параметр 2 Cycles.

В случае использования модулей DDR333 и DDR400 рекомендуется активировать параметр 3 Cycles (3 цикла таймера). Описанные рекомендации являются значениями по умолчанию, которые отображены также в спецификации JEDEC.

Если в работе операционной системы будут наблюдаться неполадки, следует отрегулировать данный тайминг, уменьшив или увеличив его длительность.

Про тайминги популярно

Про тайминги популярно.

Статья рассказывает о таймингах и их применении, и призвана детально объяснить значение этого термина.

В форумах, да и в статьях, посвященных обзорам компьютерных комплектующих с собственной оперативной памятью, нередко видишь упоминания про тайминги. Их огромное количество. Поначалу у новичка даже глаза разбегаются. А опытный человек часто просто оперирует понятиями, иногда совершенно не догадываясь, что они означают. В данной статье я постараюсь восполнить этот пробел.

Про тайминги популярно.

Статья рассказывает о таймингах и их применении, и призвана детально объяснить значение этого термина.

В форумах, да и в статьях, посвященных обзорам компьютерных комплектующих с собственной оперативной памятью, нередко видишь упоминания про тайминги. Их огромное количество. Поначалу у новичка даже глаза разбегаются. А опытный человек часто просто оперирует понятиями, иногда совершенно не догадываясь, что они означают. В данной статье я постараюсь восполнить этот пробел.

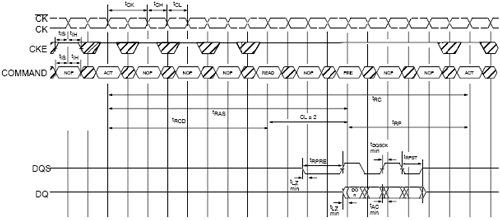

Итак, алгоритм считывания данных из памяти таков:

1)выбранный банк активируется подачей сигнала RAS;

2)данные из выбранной строки передаются в усилитель, причем на передачу данных необходима задержка (она называется RAS-to-CAS);

3)подается сигнал CAS для выбора слова из этой строки;

4)данные передаются на шину (откуда идут в контроллер памяти), при этом также происходит задержка (CAS Latency);

5)следующее слово идет уже без задержки, так как оно содержится в подготовленной строке;

6)после завершения обращения к строке происходит закрытие банка, данные возвращаются в ячейки и банк перезаряжается (задержка называется RAS Precharge).

Как видите, для совершения некоторых операций системе нужны задержки, иначе она не успеет считать выбранные данные или, например, перезарядить банк. Эти задержки и называются таймингами.

Заглянув в BIOS

Для оперативной памяти существует громадное количество задержек. Достаточно заглянуть в любое описание памяти. Но основные можно увидеть в диагностической утилите CPU-Z или в BIOS. Познакомимся поподробнее с каждым из них. Для разгона, конечно, нужно уменьшить время задержек, поэтому чем их значения меньше, тем быстрее работает система. Впрочем, о разгоне поговорим позже. В разных источниках названия могут меняться, поэтому надо смотреть на краткое обозначение.

Возьмем, для примера, скриншот из программы CPU-Z.

RAS# to CAS# Delay (Trcd)

Число тактов, необходимых для поступления данных в усилитель. (п.2 алгоритма) Другими словами, это временной интервал между командами RAS и CAS, поскольку архитектура SDRAM не позволяет подавать их одновременно.

RAS# Precharge (TRP)

Время, необходимое на перезарядку ячеек памяти после закрытия банка (п.6)

Row Active Time (TRAS)

Время, в течение которого банк остается открытым и не требует перезарядки. Изменяется вместе со следующим параметром.

Это основные тайминги, которые позволяет выставить большинство материнских плат. Однако поясню и другие.

DRAM Idle Timer

Время простаивания открытой страницы для чтения из нее данных.

Row to Column (Read/Write) (Trcd, TrcdWr, TrcdRd)

Данный параметр связан с параметром RAS-to-CAS (Trcd) и является как бы его уточнением, поскольку вычисляется по формуле Trcd(Wr/Rd) = RAS-to-CAS delay + rd/wr command delay. Второе слагаемое определяет задержку на выполнение записи/чтения. Но эта величина нерегулируемая, и изменить её нельзя. Поэтому её часто именуют просто RAS-to-CAS Delay.

Перечисленные параметры могут показаться нагромождением букв и цифр, но я уверяю, если вы заглянете хотя бы в один даташит (ближе к его концу), то быстро во всем разберетесь.

Тайминги видеокарт

В начале статьи я не зря упоминал про устройства с собственной оперативной памятью. Таковым явяется и видеокарта. И у этой памяти тоже есть тайминги достаточно заглянуть в раздел Timings популярной программы ATI Tray Tools.

Здесь возможностей для их изменения гораздо больше. Однако при заглядывании в даташит мы можем серьёзно озадачиться:

Здесь приведены ключевые, по мнению разработчиков памяти, параметры.

Поначалу кажется, что разработчики программы так не думают. Например, в ней нет тайминга tDAL, и ни в одном даташите нет таймингов tW2R, tR2R. Здесь я постараюсь объяснить значения таймингов для твикера и для даташита. Тайминги могут повторяться с приведенными выше. Их обозначения могут дополняться. Итак, начнем.

Write Latency (tWL)

Количество тактов, необходимое для произведения операции записи в память.

CAS Latency (tCL)

Задержка данных перед выдачей на шину. Подробнее см. выше. на пункт CAS Latency оперативной памяти.

CMD Latency

Задержка между подачей команды на память и ее приемом.

Strobe Latency

Задержка при посылке строб-импульса (селекторного импульса).

Activate to Read/Write, RAS to CAS Read/Write Delay, RAW Address to Column Address for Read/Write (tRCDRd/tRCDWr)

Повторюсь здесь еще раз. Для видеокарт это объяснение справедливей.

Данный параметр связан с параметром RAS-to-CAS (Trcd) и является как бы его уточнением, поскольку вычисляется по формуле Trcd(Wr/Rd) = RAS-to-CAS delay + rd/wr command delay. Второе слагаемое определяет задержку на выполнение записи/чтения. Но эта величина нерегулируемая, и изменить её нельзя. Поэтому её часто именуют просто RAS-to-CAS Delay.

Row Precharge Time, Precharge to Activate, RAS# Precharge (tRP)

Время перезарядки ячеек после закрытия банка.

Activate to Precharge, Row Active Time (tRAS)

Время, в течение которого банк остается открытым и не требует перезарядки.

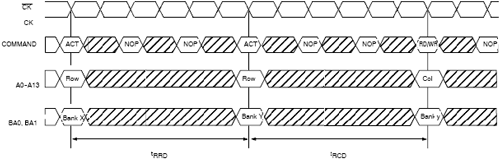

Activate to Activate, Row Active to Row Active (tRRD)

Задержка между активациями различных рядов

Auto Precharge Write Recovery + Precharge Time (tDAL)

Загадочный даташитный тайминг tDAL вызывал в формуах много споров, что он обозначает, однако в одном из документов JEDEC черным по белому написано следующее:

Write to Read Turnaround Time for Same Bank (tW2RSame Bank)

Аналогичная предыдущей процедура, отличающаяся от нее только тем, что действие происходит в том же банке. Особенность задержки в том, что процедура записи, естественно, не может быть больше промежутка до перезарядки банка (tWR), то есть заканчиваться во время перезарядки.

Read to Read Turnaround Time (tR2R)

Задержка при прерывании операции чтения операцией чтения из другого банка.

Row Cycle Time, Activate to Activate/Refresh Time, Active to Active/Auto Refresh Time (tRC)

Время для автоматической подзарядки. Встречается в даташитах.

Auto Refresh Row Cycle Time, Refresh to Activate/Refresh Command Period, Refresh Cycle Time, Refresh to Active/Refresh Comand Period (tRFC)

Минимальный промежуток между командой на подзарядку (Refresh) и либо следующей командой на подзарядку, либо командой на активацию.

Memory Refresh Rate

Частота обновления памяти.

Практика

Итак, мы рассмотрели основные тайминги, которые могут чаще всего встретиться нам в программах или даташитах. Теперь, для полной картины, я расскажу, чем полезны тайминги в разгоне.

Я же решил исследовать влияние таймингов на своей системе.

Итак, вот она:

| Процессор | Intel Celeron 1100A Tualatin 1100@1580 |

| Материнская плата | JetWay i815-EPDA |

| Память | 512Mb (2×256) PC133 NCP (FSB:DRAM=1:1) |

| Видеокарта | GeCube RadeOn 9550 Ultra (400/400) |

| Блок питания | Power Master 250W FA-5-2 |

| Жесткий диск | WD W800JB 80Gb 8Mb cache |

| Операционная система | Windows XP SP2 |

Система была оставлена «как есть». Видеокарта также не разгонялась. Испытания проводились в двух тестовых пакетах и в одной игре:

- 3DMark 2001 patch 360, так как оценивает разгон каждого элемента системы, а не только видеокарты

«Оверклокерская» для своего времени память NCP и сей раз не дала промаху и позволила запуститься на частоте 143МГц с таймингами 2-2-2-7! Но поменять последний параметр (Tras) память не дает ни по какому поводу, только с уменьшением частоты. Впрочем, это не самый важный параметр.

Как видите, понижение таймингов дает прирост производительности около 10%. И если на моей системе это не так заметно, то на более мощной различие уже становится очевидным. А если поменять еще тайминги на видеокарте, где разгон часто упирается не в память, а как раз в задержки, то труд будет более чем оправдан. А что именно меняете, теперь вы уже знаете.

Что такое тайминги?

Сегодня мы поговорим о наиболее точном определении таймингов и подтаймингов. Большинство статей в сети обладают ошибками и неточностями, а в очень достойных материалах не всегда рассмотрены все тайминги. Мы же постараемся восполнить этот пробел и дать как можно полную характеристику тем или иным временным задержкам.

Теперь разберем каждый по очереди. Схема таймингов включает в себя задержки CL-Trcd-Trp-Tras соответственно. Для работы с памятью необходимо для начала выбрать чип, с которым мы будем работать. Делается это командой CS# (Chip Select). Затем выбирается банк и строка. Перед началом работы с любой строкой необходимо ее активировать. Делается это командой выбора строки RAS# (при выборе строки она активируется). Затем (при операции линейного чтения) нужно выбрать столбец командой CAS# (эта же команда инициирует чтение). Затем считать данные и закрыть строку, совершив предварительный заряд (precharge) банка.

Тайминги расположены по порядку следования в простейшем запросе (для простоты понимания). Сначала идут тайминги, затем подтайминги.

Это все основные тайминги. Остальные тайминги имеют меньшее влияние на производительность, а потому их называют подтаймингами.

Надеемся, что представленная нами информация поможет вам разобраться в обозначении таймингов памяти, насколько они важны и за какие параметры они отвечают.

Что такое тайминги?

Для того чтобы начать изучение вопросов, посвящённых таймингам, следует узнать, как же, собственно, работает оперативная память. Ознакомиться с принципом я предлагаю в вышеупомянутой статье Enot. Выясним, что структура памяти напоминает таблицу, где сначала выбирают строку, а затем столбец; и что таблица эта разбита на банки, для памяти плотностью меньше 64Мбит (SDRAM) количеством 2 штуки, выше – 4 (ста.

Для того чтобы начать изучение вопросов, посвящённых таймингам, следует узнать, как же, собственно, работает оперативная память. Ознакомиться с принципом я предлагаю в вышеупомянутой статье Enot. Выясним, что структура памяти напоминает таблицу, где сначала выбирают строку, а затем столбец; и что таблица эта разбита на банки, для памяти плотностью меньше 64Мбит (SDRAM) количеством 2 штуки, выше – 4 (стандартно). Спецификация память DDR2 SDRAM с чипами плотностью 1Гбит предусматривает уже 8 банков.

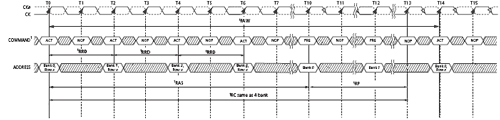

Также стоит упомянуть, что на открытие строки в используемом банке уходит больше времени, нежели в другом (т.к. используемую строку нужно сначала закрыть). Очевидно, что лучше новую строку открывать в новом банке (на этом основан принцип чередования строк).

Обычно на памяти (или в спецификации к ней) есть надпись вида 3-4-4-8 или 5-5-5-15. Это сокращённая запись (так называемая схема таймингов) основных таймингов памяти. Что же такое тайминги? Очевидно, что ни одно устройство не может работать с бесконечной скоростью. Значит, на выполнение любой операции уходит какое-либо время. Тайминги это задержка, устанавливающая время, необходимое на выполнение какой-либо команды, то есть время от отправки команды до её выполнения. А каждая цифра обозначает, какое именно время необходимо.

Теперь разберём каждый по очереди. Схема таймингов включает в себя задержки CL-Trcd-Trp-Tras соответственно.

Если вы внимательно читали статью, то узнали, что для работы с памятью необходимо для начала выбрать чип, с которым мы будем работать. Делается это командой CS# (Chip Select). Затем выбирается банк и строка. Перед началом работы с любой строкой необходимо её активировать. Делается это командой выбора строки RAS# (при выборе строки она активируется). Затем (при операции линейного чтения) нужно выбрать столбец командой CAS# (эта же команда инициирует чтение). Затем считать данные и закрыть строку, совершив предварительный заряд (precharge) банка.

Тайминги расположены по порядку следования в простейшем запросе (для простоты понимания). Сначала идут тайминги, затем подтайминги.

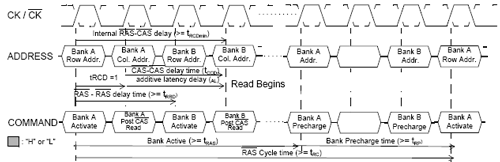

CL, Cas Latency – минимальное время между подачей команды на чтение (CAS) и началом передачи данных (задержка чтения).

Tras, Active to Precharge – минимальное время активности строки, то есть минимальное время между активацией строки (её открытием) и подачей команды на предзаряд (начало закрытия строки). Строка не может быть закрыта раньше этого времени.

Trp, Row Precharge – время, необходимое для предварительного заряда банка (precharge). Иными словами, минимальное время закрытия строки, после чего можно активировать новую строку банка.

CR, Command Rate 1/2T – Время, необходимое для декодирования контроллером команд и адресов. Иначе, минимальное время между подачей двух команд. При значении 1T команда распознаётся 1 такт, при 2T – 2 такта, 3T – 3 такта (пока только на RD600).

Это всё основные тайминги. Остальные тайминги имеют меньшее влияние на производительность, а потому их называют подтаймингами.

Trc, Row Cycle Time, Activate to Activate/Refresh Time, Active to Active/Auto Refresh Time – минимальное время между активацией строк одного банка. Является комбинацией таймингов Tras+Trp – минимального времени активности строки и времени её закрытия (после чего можно открывать новую).

Trfc, Row Refresh Cycle Time, Auto Refresh Row Cycle Time, Refresh to Activate/Refresh Command Period, – минимальное время между командой на обновление строки и командой активизации, либо другой командой обновления.

Trrd, ACTIVE bank A to ACTIVE bank B command, RAS to RAS Delay, Row Active to Row Active – минимальное время между активацией строк разных банков. Архитектурно открывать строку в другом банке можно сразу за открытием строки в первом банке. Ограничение же чисто электрическое – на активацию уходит много энергии, а потому при частых активациях строк очень высока электрическая нагрузка на цепи. Чтобы её снизить, была введена данная задержка. Используется для реализации функции чередования доступа к памяти (interleaving).

RTW, Read To Write, (Same) Rank Read To Write – минимальное время между окончанием операции чтения и подачей команды на запись, в одном ранке.

Different Rank Write to Write Delay – минимальное время между двумя командами на запись в разных ранках.

Same Rank Read To Read Delayed – минимальная задержка между двумя командами на чтение в одном ранке.

Trtp, Read to Precharge – минимальный интервал между подачей команды на чтение до команды на предварительный заряд.

Precharge to Precharge – минимальное время между двумя командами предварительного заряда.

Tpall_rp, Precharge All to Active Delay – задержка между командой Precharge All и командой на активацию строки.

Same Rank PALL to REF Delayed – устанавливает минимальное время между командой Precharge All и Refresh в одном ранке.

Different Rank REF to REF Delayed – устанавливает минимальную задержку между двумя командами на обновление (refresh) в разных ранках.

Twcl, Write Latency – задержка между подачей команды на запись и сигналом DQS. Аналог CL, но для записи.

Tdal, цитата из JEDEC 79-2C, p.74: auto precharge write recovery + precharge time (Twr+Trp).

Trcd_rd/Trcd_wr, Activate to Read/Write, RAS to CAS Read/Write Delay, RAW Address to Column Address for Read/Write – сочетание двух таймингов – Trcd (RAS to CAS) и rd/wr command delay. Именно последним и объясняется существование разных Trcd – для записи и чтения (Nf2) и установки BIOS – Fast Ras to Cas.

Tck, Clock Cycle Time – период одного такта. Именно он и определяет частоту памяти. Считается она следующим образом: 1000/Tck=X Mhz (реальная частота).

CS, Chip Select – время, необходимое на выполнения команды, подаваемой сигналом CS# для выбора нужного чипа памяти.

Tac, DQ output access time from CK – время от фронта такта до выдачи данных модулем.

Address and Command Setup Time Before Clock, время, на которое передача установок адресов команд будет предшествовать восходящему фронту такта.

Address and Command Hold Time After Clock, время, на которое будут “заперты” установки адреса и команд после нисходящего фронта такта.

Data Input Setup Time Before Clock, Data Input Hold Time After Clock, то же, что и вышеуказанные, но для данных.

Tck max, SDRAM Device Maximum Cycle Time – максимальный период цикла устройства.

Tdqsq max, DDR SDRAM Device DQS-DQ Skew for DQS and associated DQ signals – максимальный сдвиг между стробом DQS и связанными с ним сигналами данных.

Tqhs, DDR SDRAM Device Read Data Hold Skew Factor – максимальный сдвиг “запирания” считанных данных.

Tch, Tcl, CK high/low pulse width – длительность высокого/низкого уровня тактовой частоты CK.

Thp, CK half pulse width – длительность полупериода тактовой частоты CK.

Max Async Latency – максимальное время асинхронной задержки. Параметр управляет длительностью асинхронной задержки, зависящей от времени, необходимого для передачи сигнала от контроллера памяти до самого дальнего модуля памяти и обратно. Опция существует в процессорах фирмы AMD (Athlon\Opteron).

DRAM Read Latch Delay – задержка, устанавливающая время, необходимое для “запирания” (однозначного распознавания) конкретного устройства. Актуально при повышении нагрузки (числа устройств) на контроллер памяти.

Trpre, Read preamble – время, в течение которого контроллер памяти откладывает активацию приёма данных перед чтением, во избежание повреждения данных.

Trpst, Twpre, Twpst, Write preamble, read postamble, write postamble – то же для записи и после приёма данных.

Read\write Queue Bypass – определяет число раз, которое самый ранний запрос в очереди может быть обойден контроллером памяти, прежде чем быть выполненным.

Bypass Max – определяет, сколько раз самая ранняя запись в DCQ может быть обойдена, прежде чем выбор арбитра будет аннулирован. При установке в 0 выбор арбитра всегда учитывается.

SDRAM MA Wait State, Read Wait State установка 0—2-тактного опережения адресной информации перед подачей сигнала CS#.

Turn-Around Insertion – задержка между циклами. Добавляет задержку в такт между двумя последовательными операциями чтения/записи.

DRAM R/W Leadoff Timing, rd/wr command delay – задержка перед выполнением команды чтения/записи. Обычно составляет 8/7 или 7/5 тактов соответственно. Время от подачи команды до активации банка.

Speculative Leadoff, SDRAM Speculative Read. Обычно в память поступает сначала адрес, затем команда на чтение. Поскольку на расшифровку адреса уходит относительно много времени, можно применить упреждающий старт, подав адрес и команду подряд, без задержки, что повысит эффективность использования шины и снизит простои.

Twtr Same Bank, Write to Read Turnaround Time for Same Bank – время между прекращением операции записи и подачей команды на чтение в одном банке.

Tfaw, Four Active Windows – минимальное время активности четырех окон (активных строк). Применяется в восьмибанковых устройствах.

Memory Refresh Rate. Частота обновления памяти.

Также хотелось бы упомянуть о самом главном вопросе – вопросе об источниках. Именно от его качества и зависит то, насколько точным будет материал. Утверждением всех стандартов оперативной памяти занимается организация JEDEC, поэтому вопрос о компетентности снимается. Исключением являются последние материалы (Intel, Dron’t), обладающие рядом неточностей и опечаток, которые использовались как вспомогательные.

Использованные материалы:

1. DDR SDRAM «JEDEC SOLID STATE TECHNOLOGY ASSOCIATION JESD79E May 2005 Double Data Rate (DDR) SDRAM Specification (Revision of JESD79D)»

2. DDR2 SDRAM SPECIFICATION JEDEC SOLID STATE TECHNOLOGY ASSOCIATION JESD79-2C (Revision of JESD79-2B) MAY 2006

3. 4_01_02_04R13 Appendix D, Rev. 1.0 : SPD’s for DDR SDRAM

4. Intel® 965 Express Chipset Family Datasheet

Хотелось выразить благодарность Keper, по просьбе которого и была написана статья.

Обсуждение статьи ведётся в теме конференции.

Dram write recovery time что это

Опция Write Recovery Time определяет количество тактов между окончанием операции записи в оперативную память и началом регенерации.

Auto (или By SPD) – автоматическое определение количества тактов, исходя из информации о режимах работы ОЗУ из микросхемы SPD;

9 DRAM Clocks; 10 DRAM Clocks; 11 DRAM Clocks; 12 DRAM Clocks; 13 DRAM Clocks; 14 DRAM Clocks; 15 DRAM Clocks; – количество тактов между окончанием операции записи и началом регенерации.

Опция также может иметь другие названия:

(Twr) Write Recovery Time

DRAM Write Recovery Time

Write Recovery Time (tWR)

Write recovery time (Twr)

Примечание 1. Оперативная память (Random Access Memory, RAM, системная память) – это энергозависимая компьютерная память, которая предназначена для временного хранения активных программ и данных, используемых процессором во время выполнения операций.

Примечание 2. Микросхема SPD – это специальная микросхема, в которой хранятся данные о параметрах модуля оперативной памяти (ёмкость, тип, временные характеристики, рабочее напряжение, число банков, серийный номер модуля, дату изготовления модуля). Во время включения компьютера BIOS настраивает параметры работы системной памяти, согласно информации, отображенной в микросхеме SPD.

Примечание 3. Модуль оперативной памяти (оперативное запоминающее устройство, ОЗУ) – это печатная плата с контактами, на которой расположены чипы оперативной памяти, объединенные в единую логическую схему.

Примечание 4. Регенерация – процесс восстановление заряда ячеек динамической памяти.