Динамическая память что это

Динамическая память в системах жёсткого реального времени

Существует класс приложений реального времени, для которых тяжело предсказать потребности в распределении памяти во время выполнения статически. В этот класс входят, например, встраиваемые реализации стеков некоторых коммуникационных протоколов, где поведение и распределение ресурсов определяется отчасти активностью других агентов в сети. Классический подход в таких случаях заключается в использовании блочных менеджеров памяти, выделяющих фрагменты фиксированного размера (как это сделано, например, в LwIP). Этот подход накладывает нежелательные функциональные и качественные ограничения на реализацию. В этой заметке я предлагаю точку зрения, что традиционные (не блочные) аллокаторы незаслуженно обделены вниманием разработчиков систем реального времени, делюсь соображениями по релевантным вопросам, жалуюсь на жизнь, и предлагаю улучшить положение дел.

(КДПВ – см. аннотацию к диаграмме в конце)

Неочевидность свойств алгоритмов динамического распределения памяти породила настораживающую тенденцию к лёгкому искажению действительности в документации некоторых ОСРВ, причём не последнего пошиба. Например, раздел об управлении памятью FreeRTOS обходит стороною класс аллокаторов постоянной вычислительной сложности O(1), заставляя неискушённого коллегу принять, что O(n) есть теоретический потолок. Аналогичные артефакты находятся в документации к ChibiOS (1, 2). Мы, разумеется, не станем подозревать разработчиков столь выдающихся продуктов в незнании матчасти; скорее, спишем это на свойственный людям банальный недосмотр. Приложения реального времени редко полагаются на динамическое распределение во время выполнения, так что множество затронутых здесь невелико.

Знакомому со спецификой систем реального времени читателю не нужно объяснять, что первоочередное значение для них имеют характеристики не среднего, а худшего случая, что радикально отличает их от систем общего назначения (примером последней будет та, при помощи которой вы сейчас читаете этот текст). Для прочих читателей приведу пример: если некий алгоритм имеет асимптотическую сложность O(log n) в подавляющем большинстве случаев, но раз в тысячу лет иногда выпадает случай O(n), то интерес для анализа представляет лишь последний.

Порядком вычислительной сложности дело не ограничивается. Ресурсный потолок по памяти, очевидно, имеет критическое значение для встраиваемых систем, где количество доступных мегабайт можно пересчитать пальцами одной руки. Поставщики же ОСРВ имеют наклонности к заимствованию оптимизированных на средний случай алгоритмов из продуктов, не рассчитанных на реальное время и встраиваемые приложения. Подтверждающим примером будет реализация аллокатора в NuttX, где используется стратегия поиска наилучшего совпадения (best fit), чья пониженная склонность к фрагментации в общем случае даётся ценою крайне пессимистичного её прогноза для худшего случая. Аналогичные замечания можно сделать в адрес упомянутых ранее конкурентов.

Недостаток внимания со стороны вендоров ОСРВ к теоретической стороне вопроса порождает положительную обратную связь, где неточности в документации и технически неоптимальные реализации действительно вынуждают пользователей отказываться от их использования, что снижает интерес, и, как следствие, оставляет осложнения без внимания.

Ваш покорный слуга недаром увяз в этой проблеме. Работая над реализацией встраиваемого сетевого стека для одного протокола реального времени, я обнаружил, что замена используемого на тот момент традиционного блочного менеджера памяти на обычный аллокатор фрагментов произвольного размера не только радикально упрощает API и реализацию, но и улучшает асимптотическую сложность внутренних процедур стека. Последнее обусловлено, среди прочего, заменой фрагментированных буферов из цепочек блоков на непрерывные фрагменты памяти:

На второй день углубления в релевантные материалы, черенок моего сознания наткнулся на анализ алгоритмов Buddy Allocator, Half-Fit, и Two-Level Segregated Fit (TLSF). Все они представляют собою детерминированные аллокаторы постоянной вычислительной сложности O(1) (для Buddy Allocator мы делаем допущение, что объём памяти постоянен, в противном случае оценка будет иной). Почтенные господа J. Herter и J. Robson подвергают оба ресурсных вопроса – как времени, так и памяти – детальному рассмотрению в диссертации “Timing-Predictable Memory Allocation In Hard Real-Time Systems” и статье “Worst case fragmentation of first fit and best fit storage allocation strategies”, соответственно.

Даже малознакомый с теорией динамического распределения памяти читатель найдёт обоснование постоянства вычислительной сложности приведённых алгоритмов тривиальным. Гораздо больший интерес здесь представляет фрагментация. Насколько я могу видеть, многие мои коллеги ошибочно подозревают, что динамические аллокаторы неизбежно приходят в состояние катастрофической фрагментации (где выделение памяти невозможно из-за высокого дробления свободных участков) за конечное время. Подробный разбор вопроса с доказательством обратного можно найти на страницах 26–33 диссертации многоуважаемого Хертера, здесь же я лишь оставлю финальный вывод, что предел размера кучи H, при котором катастрофическая фрагментация недостижима, для лучших из приведённых алгоритмов определён как:

Где M – пиковая потребность приложения в динамической памяти, n – размер наибольшей аллокации.

Здесь уместно вернуться к началу и бросить ещё камней в огород поставщиков ОСРВ. Как я упомянул, в некоторых продуктах встречаются реализации алгоритмов управления памятью, чья стратегия размещения предусматривает выбор свободного фрагмента минимально возможного размера. Эта стратегия хорошо показывает себя в среднем случае, но в особых условиях деградирует до теоретического предела H = M (n — 2), уничтожая надежду на её уместность во встраиваемых системах.

Для меня было очевидным, что множество задач реального времени, где разумное применение хорошо охарактеризованных (предсказуемых) алгоритмов выделения памяти является оправданным, не исчерпывается моим стеком. Контраст между этим осознанием и недостаточным вниманием сообщества разработчиков встраиваемых систем к детерминированным аллокаторам, усугублённый также сомнительными дискуссиями на StackOverflow, побудил меня спасать дело самостоятельно, и я сделал свой собственный аллокатор. Он чрезвычайно компактен (500 строк на C99/C11), его процедуры выделения и освобождения памяти имеют постоянную вычислительную сложность, и предельный уровень фрагментации хорошо охарактеризован.

Приведённая выше модель худшего случая фрагментации потребовала дополнения, потому что её общая форма не уделяет внимания собственной потребности аллокатора в памяти для хранения метаданных. Уточнённая модель, построенная с учётом специфики моей реализации, доступна в документации, здесь её не привожу по причине малой теоретической ценности. Вместо этого призываю осмотреть иллюстрацию в начале текста; её содержимое учитывает конкретику моей реализации, и оно таково:

Если величины H кажутся чрезмерными, это неспроста, ведь понятия верхнего предела и худшего случая не эквивалентны. Задача поиска огибающей худшего случая включает в себя минимизацию разрыва между теоретическим пределом и практически достижимым наихудшим состоянием. В нашем случае это конкретизируется в минимизацию разрыва между значением H, предсказанным нашей моделью, и реальным пиковым случаем фрагментации, который система может встретить на практике. Я надеялся подобраться к проблеме уменьшения H при сохранении гарантированных свойств алгоритма при помощи симуляций с систематическим перебором возможных состояний, но был вынужден отложить эту затею по причине отсутствия времени. Однако, вовлечённый в тему человек понимает высокую практическую значимость этой доработки. Если среди читателей найдутся достаточно мотивированные коллеги (Embox?), я бы с готовностью ввязался в коллаборацию по этому вопросу.

Другой важный вопрос заключается в исправлении текущего положения дел в открытых системах. Я вяло потыкал метафорической палочкой одного из разработчиков NuttX по этому поводу, и почерпнул, что вопрос имеет низкий приоритет: «I considered porting TLSF at one point, but overall it’s low on my list of NuttX improvements I’d explore if I actually had time». Есть куда стремиться.

Анатомия RAM

У каждого компьютера есть ОЗУ, встроенное в процессор или находящееся на отдельной подключенной к системе плате — вычислительные устройства просто не смогли бы работать без оперативной памяти. ОЗУ — потрясающий образец прецизионного проектирования, однако несмотря на тонкость процессов изготовления, память ежегодно производится в огромных объёмах. В ней миллиарды транзисторов, но она потребляет только считанные ватты мощности. Учитывая большую важность памяти, стоит написать толковый анализ её анатомии.

Итак, давайте приготовимся к вскрытию, выкатим носилки и отправимся в анатомический театр. Настало время изучить все подробности каждой ячейки, из которых состоит современная память, и узнать, как она работает.

Зачем же ты, RAM-ео?

Процессорам требуется очень быстро получать доступ к данным и командам, чтобы программы выполнялись мгновенно. Кроме того, им нужно, чтобы при произвольных или неожиданных запросах не очень страдала скорость. Именно поэтому для компьютера так важно ОЗУ (RAM, сокращение от random-access memory — память с произвольным доступом).

Существует два основных типа RAM: статическая и динамическая, или сокращённо SRAM и DRAM.

Мы будем рассматривать только DRAM, потому что SRAM используется только внутри процессоров, таких как CPU или GPU. Так где же находится DRAM в наших компьютерах и как она работает?

Большинству людей знакома RAM, потому что несколько её планок находится рядом с CPU (центральным процессором, ЦП). Эту группу DRAM часто называют системной памятью, но лучше её называть памятью CPU, потому что она является основным накопителем рабочих данных и команд процессора.

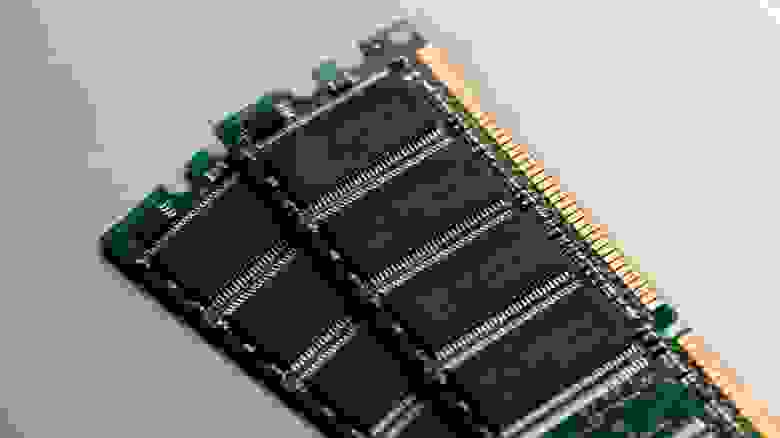

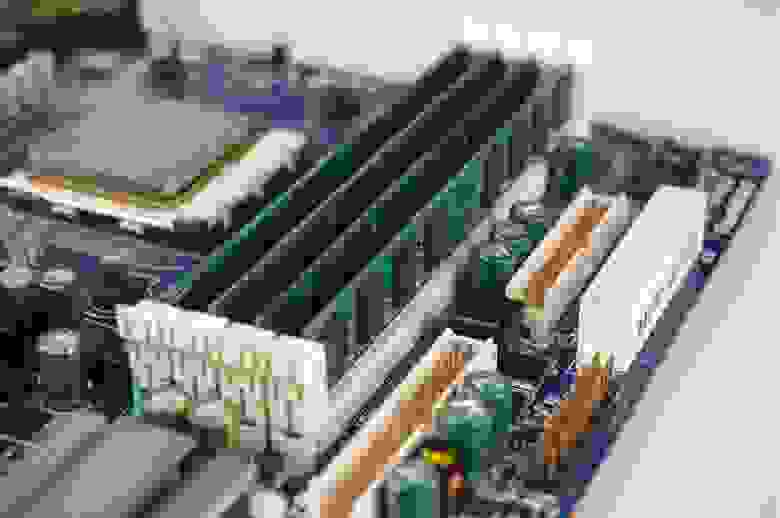

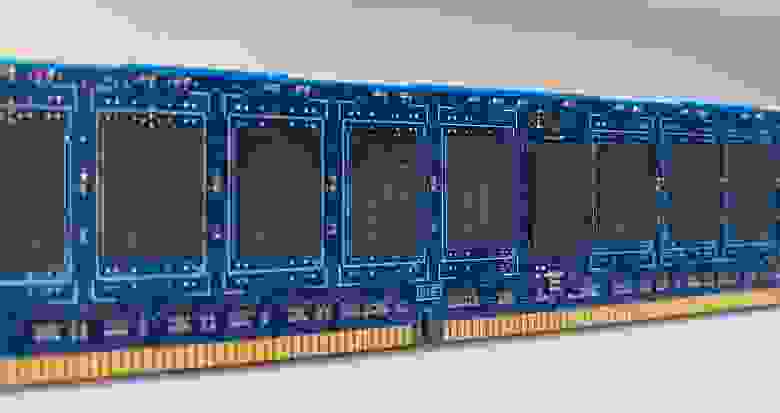

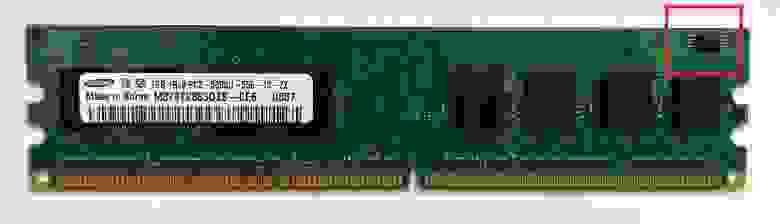

Как видно на представленном изображении, DRAM находится на небольших платах, вставляемых в материнскую (системную) плату. Каждую плату обычно называют DIMM или UDIMM, что расшифровывается как dual inline memory module (двухсторонний модуль памяти) (U обозначает unbuffered (без буферизации)). Подробнее мы объясним это позже; пока только скажем, что это самая известная RAM любого компьютера.

Она не обязательно должна быть сверхбыстрой, но современным ПК для работы с большими приложениями и для обработки сотен процессов, выполняемых в фоновом режиме, требуется много памяти.

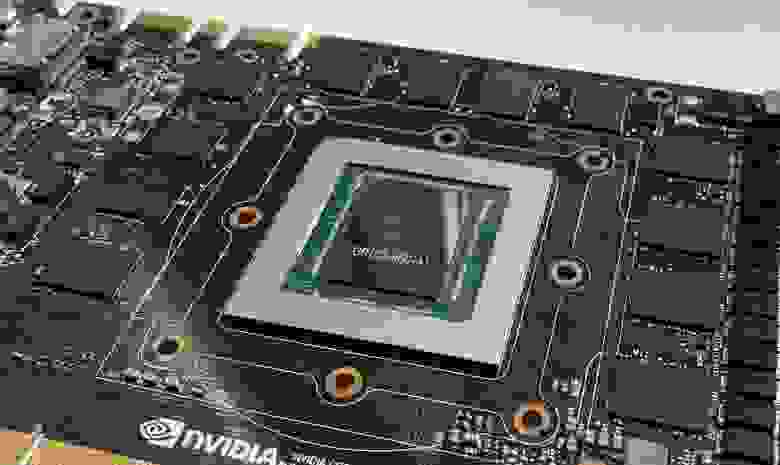

Ещё одним местом, где можно найти набор чипов памяти, обычно является графическая карта. Ей требуется сверхбыстрая DRAM, потому что при 3D-рендеринге выполняется огромное количество операций чтения и записи данных. Этот тип DRAM предназначен для несколько иного использования по сравнению с типом, применяемым в системной памяти.

Ниже вы видите GPU, окружённый двенадцатью небольшими пластинами — это чипы DRAM. Конкретно этот тип памяти называется GDDR5X, о нём мы поговорим позже.

Графическим картам не нужно столько же памяти, как CPU, но их объём всё равно достигает тысяч мегабайт.

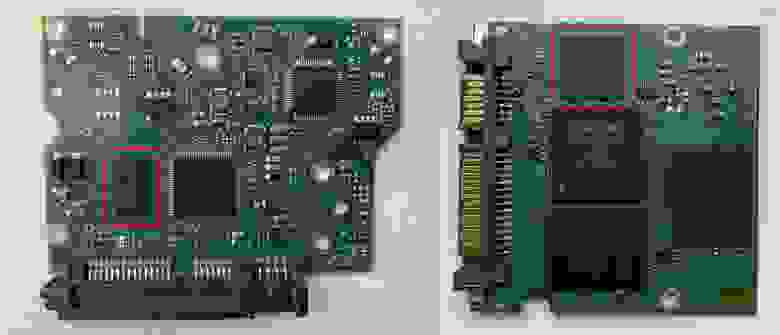

Не каждому устройству в компьютере нужно так много: например, жёстким дискам достаточно небольшого количества RAM, в среднем по 256 МБ; они используются для группировки данных перед записью на диск.

На этих фотографиях мы видим платы HDD (слева) и SSD (справа), на которых отмечены чипы DRAM. Заметили, что чип всего один? 256 МБ сегодня не такой уж большой объём, поэтому вполне достаточно одного куска кремния.

Узнав, что каждый компонент или периферийное устройство, выполняющее обработку, требует RAM, вы сможете найти память во внутренностях любого ПК. На контроллерах SATA и PCI Express установлены небольшие чипы DRAM; у сетевых интерфейсов и звуковых карт они тоже есть, как и у принтеров со сканнерами.

Если память можно встретить везде, она может показаться немного скучной, но стоит вам погрузиться в её внутреннюю работу, то вся скука исчезнет!

Скальпель. Зажим. Электронный микроскоп.

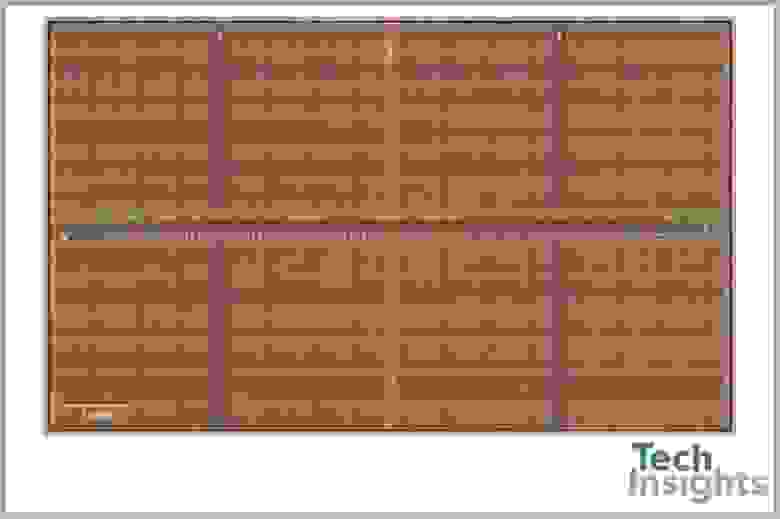

У нас нет всевозможных инструментов, которые инженеры-электронщики используют для изучения своих полупроводниковых творений, поэтому мы не можем просто разобрать чип DRAM и продемонстрировать вам его внутренности. Однако такое оборудование есть у ребят из TechInsights, которые сделали этот снимок поверхности чипа:

Если вы подумали, что это похоже на сельскохозяйственные поля, соединённые тропинками, то вы не так далеки от истины! Только вместо кукурузы или пшеницы поля DRAM в основном состоят из двух электронных компонентов:

Синими и зелёными линиями обозначены соединения, подающие напряжение на МОП-транзистор и конденсатор. Они используются для считывания и записи данных в ячейку, и первой всегда срабатывает вертикальная (разрядная) линия.

Канавочный конденсатор, по сути, используется в качестве сосуда для заполнения электрическим зарядом — его пустое/заполненное состояние даёт нам 1 бит данных: 0 — пустой, 1 — полный. Несмотря на предпринимаемые инженерами усилия, конденсаторы не способны хранить этот заряд вечно и со временем он утекает.

Это означает, что каждую ячейку памяти нужно постоянно обновлять по 15-30 раз в секунду, хотя сам этот процесс довольно быстр: для обновления набора ячеек требуется всего несколько наносекунд. К сожалению, в чипе DRAM множество ячеек, и во время их обновления считывание и запись в них невозможна.

К каждой линии подключено несколько ячеек:

Строго говоря, эта схема неидеальна, потому что для каждого столбца ячеек используется две разрядные линии — если бы мы изобразили всё, то схема бы стала слишком неразборчивой.

Полная строка ячеек памяти называется страницей, а длина её зависит от типа и конфигурации DRAM. Чем длиннее страница, тем больше в ней бит, но и тем большая электрическая мощность нужна для её работы; короткие страницы потребляют меньше мощности, но и содержат меньший объём данных.

Однако нужно учитывать и ещё один важный фактор. При считывании и записи на чип DRAM первым этапом процесса является активация всей страницы. Строка битов (состоящая из нулей и единиц) хранится в буфере строки, который по сути является набором усилителей считывания и защёлок, а не дополнительной памятью. Затем активируется соответствующий столбец для извлечения данных из этого буфера.

Если страница слишком мала, то чтобы успеть за запросами данных, строки нужно активировать чаще; и наоборот — большая страница предоставляет больше данных, поэтому активировать её можно реже. И даже несмотря на то, что длинная строка требует большей мощности и потенциально может быть менее стабильной, лучше стремиться к получению максимально длинных страниц.

Если собрать вместе набор страниц, то мы получим один банк памяти DRAM. Как и в случае страниц, размер и расположение строк и столбцов ячеек играют важную роль в количестве хранимых данных, скорости работы памяти, энергопотреблении и так далее.

Например, схема может состоять из 4 096 строк и 4 096 столбцов, при этом полный объём одного банка будет равен 16 777 216 битам или 2 мегабайтам. Но не у всех чипов DRAM банки имеют квадратную структуру, потому что длинные страницы лучше, чем короткие. Например, схема из 16 384 строк и 1 024 столбцов даст нам те же 2 мегабайта памяти, но каждая страница будет содержать в четыре раза больше памяти, чем в квадратной схеме.

Все страницы в банке соединены с системой адресации строк (то же относится и к столбцам) и они контролируются сигналами управления и адресами для каждой строки/столбца. Чем больше строк и столбцов в банке, тем больше битов должно использоваться в адресе.

Для банка размером 4 096 x 4 096 для каждой системы адресации требуется 12 бит, а для банка 16 384 x 1 024 потребуется 14 бит на адреса строк и 10 бит на адреса столбцов. Стоит заметить, что обе системы имеют суммарный размер 24 бита.

Если бы чип DRAM мог предоставлять доступ к одной странице за раз, то это было бы не особо удобно, поэтому в них упаковано несколько банков ячеек памяти. В зависимости от общего размера, чип может иметь 4, 8 или даже 16 банков — чаще всего используется 8 банков.

Все эти банки имеют общие шины команд, адресов и данных, что упрощает структуру системы памяти. Пока один банк занят работой с одной командой, другие банки могут продолжать выполнение своих операций.

Весь чип, содержащий все банки и шины, упакован в защитную оболочку и припаян к плате. Она содержит электропроводники, подающие питание для работы DRAM и сигналов команд, адресов и данных.

На фотографии выше показан чип DRAM (иногда называемый модулем), изготовленный компанией Samsung. Другими ведущими производителями являются Toshiba, Micron, SK Hynix и Nanya. Samsung — крупнейший производитель, он имеет приблизительно 40% мирового рынка памяти.

Каждый изготовитель DRAM использует собственную систему кодирования характеристик памяти; на фотографии показан чип на 1 гигабит, содержащий 8 банков по 128 мегабита, выстроенных в 16 384 строки и 8 192 столбца.

Выше по рангу

Компании-изготовители памяти берут несколько чипов DRAM и устанавливают их на одну плату, называемую DIMM. Хотя D расшифровывается как dual (двойная), это не значит, что на ней два набора чипов. Под двойным подразумевается количество электрических контактов в нижней части платы; то есть для работы с модулями используются обе стороны платы.

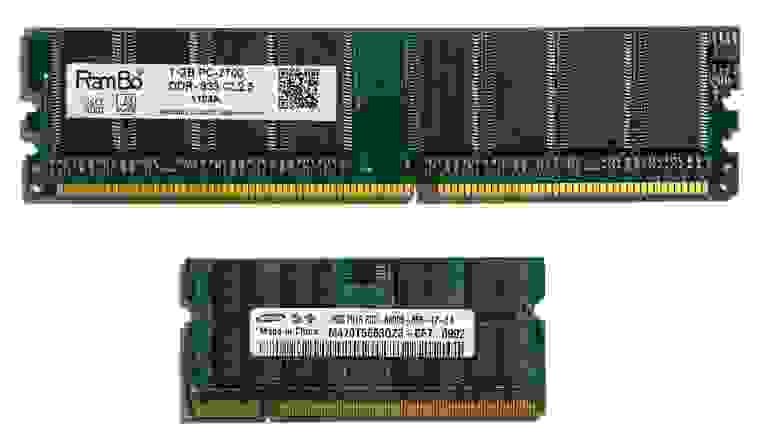

Сами DIMM имеют разный размер и количество чипов:

На фотографии сверху показана стандартная DIMM для настольного ПК, а под ней находится так называемая SO-DIMM (small outline, «DIMM малого профиля»). Маленький модуль предназначен для ПК малого форм-фактора, например, ноутбуков и компактных настольных компьютеров. Из-за малого пространства уменьшается количество используемых чипов, изменяется скорость работы памяти, и так далее.

Существует три основных причины для использования нескольких чипов памяти на DIMM:

То есть каждому DIMM, который устанавливается в компьютер с Ryzen, потребуется восемь модулей DRAM (8 чипов x 8 бит = 64 бита). Можно подумать, что графическая карта 5700 XT будет иметь 32 чипа памяти, но у неё их только 8. Что же это нам даёт?

В чипы памяти, предназначенные для графических карт, устанавливают больше банков, обычно 16 или 32, потому что для 3D-рендеринга необходим одновременный доступ к большому объёму данных.

Один ранг и два ранга

Множество модулей памяти, «заполняющих» шину данных контроллера памяти, называется рангом, и хотя к контроллеру можно подключить больше одного ранга, за раз он может получать данные только от одного ранга (потому что ранги используют одну шину данных). Это не вызывает проблем, потому что пока один ранг занимается ответом на переданную ему команду, другому рангу можно передать новый набор команд.

Платы DIMM могут иметь несколько рангов и это особенно полезно, когда вам нужно огромное количество памяти, но на материнской плате мало разъёмов под RAM.

Так называемые схемы с двумя (dual) или четырьмя (quad) рангами потенциально могут обеспечить большую производительность, чем одноранговые, но увеличение количества рангов быстро повышает нагрузку на электрическую систему. Большинство настольных ПК способно справиться только с одним-двумя рангами на один контроллер. Если системе нужно больше рангов, то лучше использовать DIMM с буферизацией: такие платы имеют дополнительный чип, облегчающий нагрузку на систему благодаря хранению команд и данных в течение нескольких циклов, прежде чем передать их дальше.

Множество модулей памяти Nanya и один буферный чип — классическая серверная RAM

Но не все ранги имеют размер 64 бита — используемые в серверах и рабочих станциях DIMM часто размером 72 бита, то есть на них есть дополнительный модуль DRAM. Этот дополнительный чип не обеспечивает повышение объёма или производительности; он используется для проверки и устранения ошибок (error checking and correcting, ECC).

Вы ведь помните, что всем процессорам для работы нужна память? В случае ECC RAM небольшому устройству, выполняющему работу, предоставлен собственный модуль.

Шина данных в такой памяти всё равно имеют ширину всего 64 бита, но надёжность хранения данных значительно повышается. Использование буферов и ECC только незначительно влияет на общую производительность, зато сильно повышает стоимость.

Жажда скорости

У всех DRAM есть центральный тактовый сигнал ввода-вывода (I/O, input/output) — напряжение, постоянно переключающееся между двумя уровнями; он используется для упорядочивания всего, что выполняется в чипе и шинах памяти.

Если бы мы вернулись назад в 1993 год, то смогли бы приобрести память типа SDRAM (synchronous, синхронная DRAM), которая упорядочивала все процессы с помощью периода переключения тактового сигнала из низкого в высокое состояние. Так как это происходит очень быстро, такая система обеспечивает очень точный способ определения времени выполнения событий. В те времена SDRAM имела тактовые сигналы ввода-вывода, обычно работавшие с частотой от 66 до 133 МГц, и за каждый такт сигнала в DRAM можно было передать одну команду. В свою очередь, чип за тот же промежуток времени мог передать 8 бит данных.

Быстрое развитие SDRAM, ведущей силой которого был Samsung, привело к созданию в 1998 году её нового типа. В нём передача данных синхронизировалась по повышению и падению напряжения тактового сигнала, то есть за каждый такт данные можно было дважды передать в DRAM и обратно.

Как же называлась эта восхитительная новая технология? Double data rate synchronous dynamic random access memory (синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных). Обычно её просто называют DDR-SDRAM или для краткости DDR.

Память DDR быстро стала стандартом (из-за чего первоначальную версию SDRAM переименовали в single data rate SDRAM, SDR-DRAM) и в течение последующих 20 лет оставалась неотъемлемой частью всех компьютерных систем.

Прогресс технологий позволил усовершенствовать эту память, благодаря чему в 2003 году появилась DDR2, в 2007 году — DDR3, а в 2012 году — DDR4. Каждая новая версия обеспечивала повышение производительности благодаря ускорению тактового сигнала ввода-вывода, улучшению систем сигналов и снижению энергопотребления.

DDR2 внесла изменение, которое мы используем и сегодня: генератор тактовых сигналов ввода-вывода превратился в отдельную систему, время работы которой задавалось отдельным набором синхронизирующих сигналов, благодаря чему она стала в два раза быстрее. Это аналогично тому, как CPU используют для упорядочивания работы тактовый сигнал 100 МГц, хотя внутренние синхронизирующие сигналы работают в 30-40 раз быстрее.

DDR3 и DDR4 сделали шаг вперёд, увеличив скорость тактовых сигналов ввода-вывода в четыре раза, но во всех этих типах памяти шина данных для передачи/получения информации по-прежнему использовала только повышение и падение уровня сигнала ввода-вывода (т.е. удвоенную частоту передачи данных).

Сами чипы памяти не работают на огромных скоростях — на самом деле, они шевелятся довольно медленно. Частота передачи данных (измеряемая в миллионах передач в секунду — millions of transfers per second, MT/s) в современных DRAM настолько высока благодаря использованию в каждом чипе нескольких банков; если бы на каждый модуль приходился только один банк, всё работало бы чрезвычайно медленно.

| Тип DRAM | Обычная частота чипа | Тактовый сигнал ввода-вывода | Частота передачи данных |

| SDR | 100 МГц | 100 МГц | 100 MT/s |

| DDR | 100 МГц | 100 МГц | 200 MT/s |

| DDR2 | 200 МГц | 400 МГц | 800 MT/s |

| DDR3 | 200 МГц | 800 МГц | 1600 MT/s |

| DDR4 | 400 МГц | 1600 МГц | 3200 MT/s |

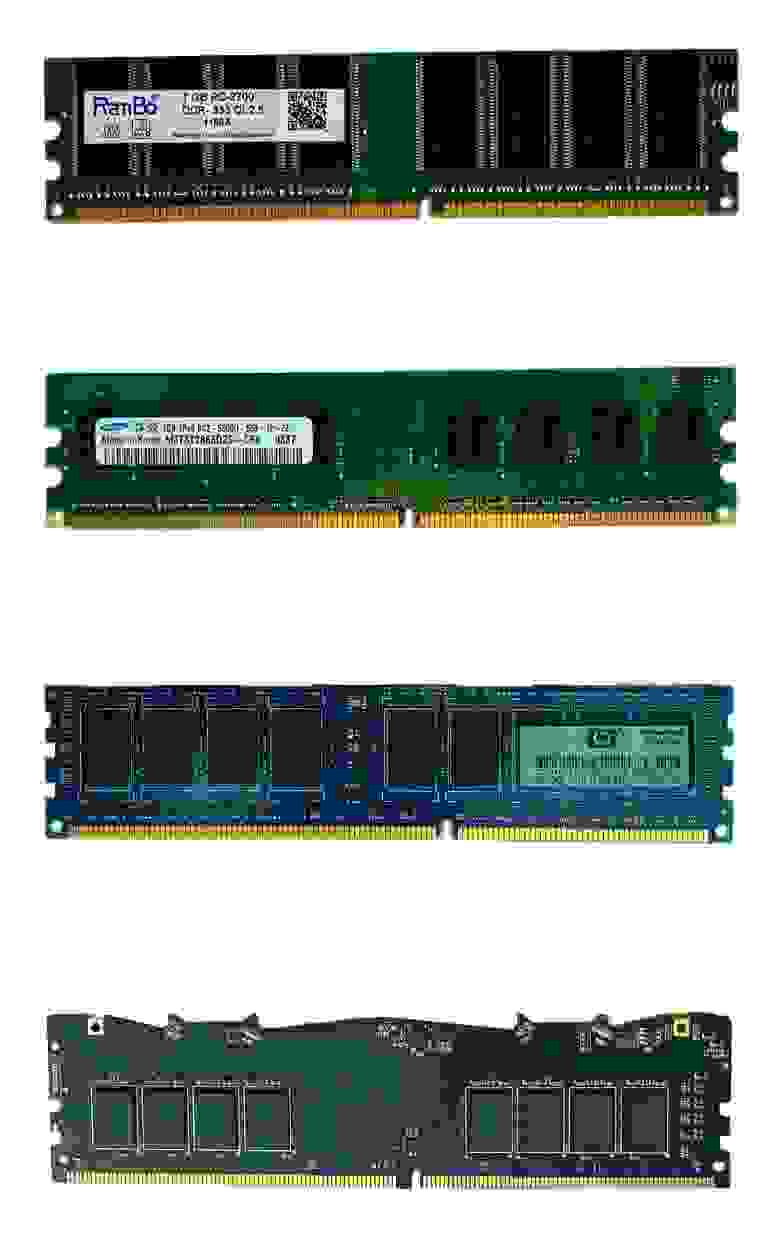

Каждая новая версия DRAM не обладает обратной совместимостью, то есть используемые для каждого типа DIMM имеют разные количества электрических контактов, разъёмы и вырезы, чтобы пользователь не мог вставить память DDR4 в разъём DDR-SDRAM.

Сверху вниз: DDR-SDRAM, DDR2, DDR3, DDR4

DRAM для графических плат изначально называлась SGRAM (synchronous graphics, синхронная графическая RAM). Этот тип RAM тоже подвергался усовершенствованиям, и сегодня его для понятности называют GDDR. Сейчас мы достигли версии 6, а для передачи данных используется система с учетверённой частотой, т.е. за тактовый цикл происходит 4 передачи.

| Тип DRAM | Обычная частота памяти | Тактовый сигнал ввода-вывода | Частота передачи данных |

| GDDR | 250 МГц | 250 МГц | 500 MT/s |

| GDDR2 | 500 МГц | 500 МГц | 1000 MT/s |

| GDDR3 | 800 МГц | 1600 МГц | 3200 MT/s |

| GDDR4 | 1000 МГц | 2000 МГц | 4000 MT/s |

| GDDR5 | 1500 МГц | 3000 МГц | 6000 MT/s |

| GDDR5X | 1250 МГц | 2500 МГц | 10000 MT/s |

| GDDR6 | 1750 МГц | 3500 МГц | 14000 MT/s |

Кроме более высокой частоты передачи, графическая DRAM обеспечивает дополнительные функции для ускорения передачи, например, возможность одновременного открытия двух страниц одного банка, работающие в DDR шины команд и адресов, а также чипы памяти с гораздо большими скоростями тактовых сигналов.

Какой же минус у всех этих продвинутых технологий? Стоимость и тепловыделение.

Один модуль GDDR6 примерно вдвое дороже аналогичного чипа DDR4, к тому же при полной скорости он становится довольно горячим — именно поэтому графическим картам с большим количеством сверхбыстрой RAM требуется активное охлаждение для защиты от перегрева чипов.

Скорость битов

Производительность DRAM обычно измеряется в количестве битов данных, передаваемых за секунду. Ранее в этой статье мы говорили, что используемая в качестве системной памяти DDR4 имеет чипы с 8-битной шириной шины, то есть каждый модуль может передавать до 8 бит за тактовый цикл.

То есть если частота передачи данных равна 3200 MT/s, то пиковый результат равен 3200 x 8 = 25 600 Мбит в секунду или чуть больше 3 ГБ/с. Так как большинство DIMM имеет 8 чипов, потенциально можно получить 25 ГБ/с. Для GDDR6 с 8 модулями этот результат был бы равен 440 ГБ/с!

Обычно это значение называют полосой пропускания (bandwidth) памяти; оно является важным фактором, влияющим на производительность RAM. Однако это теоретическая величина, потому что все операции внутри чипа DRAM не происходят одновременно.

Чтобы разобраться в этом, давайте взглянем на показанное ниже изображение. Это очень упрощённое (и нереалистичное) представление того, что происходит, когда данные запрашиваются из памяти.

На первом этапе активируется страница DRAM, в которой содержатся требуемые данные. Для этого памяти сначала сообщается, какой требуется ранг, затем соответствующий модуль, а затем конкретный банк.

Чипу передаётся местоположение страницы данных (адрес строки), и он отвечает на это передачей целой страницы. На всё это требуется время и, что более важно, время нужно и для полной активации строки, чтобы гарантировать полную блокировку строки битов перед выполнением доступа к ней.

Затем определяется соответствующий столбец и извлекается единственный бит информации. Все типы DRAM передают данные пакетами, упаковывая информацию в единый блок, и пакет в современной памяти почти всегда равен 8 битам. То есть даже если за один тактовый цикл извлекается один бит, эти данные нельзя передать, пока из других банков не будет получено ещё 7 битов.

А если следующий требуемый бит данных находится на другой странице, то перед активацией следующей необходимо закрыть текущую открытую страницу (это процесс называется pre-charging). Всё это, разумеется, требует больше времени.

Все эти различные периоды между временем отправки команды и выполнением требуемого действия называются таймингами памяти или задержками. Чем ниже значение, тем выше общая производительность, ведь мы тратим меньше времени на ожидание завершения операций.

Некоторые из этих задержек имеют знакомые фанатам компьютеров названия:

| Название тайминга | Описание | Обычное значение в DDR4 |

| tRCD | Row-to-Column Delay: количество циклов между активацией строки и возможностью выбора столбца | 17 циклов |

| CL | CAS Latency: количество циклов между адресацией столбца и началом передачи пакет данных | 15 циклов |

| tRAS | Row Cycle Time: наименьшее количество циклов, в течение которого строка должна оставаться активной перед тем, как можно будет выполнить её pre-charging | 35 циклов |

| tRP | Row Precharge time: минимальное количество циклов, необходимое между активациями разных строк | 17 циклов |

Существует ещё много других таймингов и все их нужно тщательно настраивать, чтобы DRAM работала стабильно и не искажала данные, имея при этом оптимальную производительность. Как можно увидеть из таблицы, схема, демонстрирующая циклы в действии, должна быть намного шире!

Хотя при выполнении процессов часто приходится ждать, команды можно помещать в очереди и передавать, даже если память занята чем-то другим. Именно поэтому можно увидеть много модулей RAM там, где нам нужна производительность (системная память CPU и чипы на графических картах), и гораздо меньше модулей там, где они не так важны (в жёстких дисках).

Тайминги памяти можно настраивать — они не заданы жёстко в самой DRAM, потому что все команды поступают из контроллера памяти в процессоре, который использует эту память. Производители тестируют каждый изготавливаемый чип и те из них, которые соответствуют определённым скоростям при заданном наборе таймингов, группируются вместе и устанавливаются в DIMM. Затем тайминги сохраняются в небольшой чип, располагаемый на плате.

Даже памяти нужна память. Красным указано ПЗУ (read-only memory, ROM), в котором содержится информация SPD.

Процесс доступа к этой информации и её использования называется serial presence detect (SPD). Это отраслевой стандарт, позволяющий BIOS материнской платы узнать, на какие тайминги должны быть настроены все процессы.

Многие материнские платы позволяют пользователям изменять эти тайминги самостоятельно или для улучшения производительности, или для повышения стабильности платформы, но многие модули DRAM также поддерживают стандарт Extreme Memory Profile (XMP) компании Intel. Это просто дополнительная информация, хранящаяся в памяти SPD, которая сообщает BIOS: «Я могу работать с вот с такими нестандартными таймингами». Поэтому вместо самостоятельной возни с параметрами пользователь может настроить их одним нажатием мыши.

Спасибо за службу, RAM!

В отличие от других уроков анатомии, этот оказался не таким уж грязным — DIMM сложно разобрать и для изучения модулей нужны специализированные инструменты. Но внутри них таятся потрясающие подробности.

Возьмите в руку планку памяти DDR4-SDRAM на 8 ГБ из любого нового ПК: в ней упаковано почти 70 миллиардов конденсаторов и такое же количество транзисторов. Каждый из них хранит крошечную долю электрического заряда, а доступ к ним можно получить за считанные наносекунды.

Даже при повседневном использовании она может выполнять бесчисленное количество команд, и большинство из плат способны без малейших проблем работать многие годы. И всё это меньше чем за 30 долларов? Это просто завораживает.

DRAM продолжает совершенствоваться — уже скоро появится DDR5, каждый модуль которой обещает достичь уровня полосы пропускания, с трудом достижимый для двух полных DIMM типа DDR4. Сразу после появления она будет очень дорогой, но для серверов и профессиональных рабочих станций такой скачок скорости окажется очень полезным.