Dram rapl bwlimit что это в биосе

BIOS M3A32-MVP Deluxe

В данной статье я собрал информацию о некоторых настройках BIOS материнской платы M3A32-MVP Deluxe. А точнее о тех из них, которые интересны при разгоне. Все, что сказано ниже не является абсолютной истиной и было собрано из различных источников, в большинстве своем англоязычных. Поэтому выношу этот материал на обсуждение. Тем более, что сам хотел бы узнать побольше о некоторых опциях. Личное мнение от использования тех или иных настроек я записывал под знаком *. Вот подходящая ветка на оверах, где можно и нужно обсудить данный материал. Осталось добавить, что на данной МП я разгонял Athlon 64 x2 4400+ Brisbane, поэтому, возможно список опций неполный по сравнению с использованием Phenom-ов.

Jumper Free Configuration

AI Overclocking [Manual]

Установка значения Manual открывает Вашему взору следующие опции:

FSB Frequency [200-600 MHz]

Значение, которое наряду с множителем задает устанавливает частоту процессора. Например, 200 FSB x 11 = 2.2 Ггц.

PCIE Frequency [100-150 MHz]

Рекомендуется устанавливать не более 115-118 МГц, при этом можно добиться небольшого увеличения производительности в 3D-приложениях. Установка значений превышающие данные может вызвать проблемы в работе южного и северного мостов и, как следствие, проблемы в работе периферии и жестких дисков, но кого этим испугаешь 😉

Processor Frequency Multiplier [x4 — x11,5]

В режиме AI Overclocking Auto BIOS устанавливает заданную по умолчанию частоту CPU. В режиме Manual можно задать множитель из приведенного интервала.

Processor Voltage [0,8-1,6875 v]

Устанавливается с шагом 0,0125v.

* Минимальное напряжение на котором процессор (вышеназванный Athlon) завелся и даже прошел 30 мин. тест стабильности ОССТ 2.0.0 было 1,025v. В CPU-Z 1.44 значение напряжения сильно занижено по сравнению с выставленным в BIOS (разница 0,017v). SpeedFan напряжение показывает такое же как и в BIOS с округлением до 2-го знака. В Everest тоже. Видимо брешет CPU-Z. Значения более 1,6v подсвечиваются красным и увеличение с 1,6 вплоть до 1,6875v прироста в разгоне и стабильности не приносит.

CPU-NB HT Link Speed [200-1000MHz]

Частота HT для Phenom-ов от 200 до 2200МНz

CPU VDDA Voltage [2,5-2,8v]

* Толкового объяснения в русскоязычном интернете не нашел. По поиску нашел на одном из англоязычных форумов объяснение, что этот параметр устанавливает схему регулирования центрального процессора и манипуляциями с ним можно добиться стабильности при разгоне. Проверил, действительно, на комп на пределе разгона (проц Athlon 64 x2 Brisbane 4400+ @ 3300Гц 1,6v) при значении данной опции 2,5v грузился через раз, а при установке ее в 2,8v он у меня прошел SuperPi32M, правда, ОССТ не выдержал. При этом, помогло именно значение 2,8v, с 2,6 и 2,7 была та же картина, что и с 2,5.

DDR Voltage [1,8-2,5v]

* устанавливается с шагом 0,02v. Значения 2,2v и выше подсвечиваются красным.

NorthBridge Voltage [Manual]

Данная установка открывает следующие опции:

Hyper Transport Voltage [1,2-1,5v]

Выставляет напряжение на шине Hyper Transport.

* При разгоне ставил 1,3v.

Southbridge Voltage [1,2-1,4v]

* При разгоне выставил 1,3v.

Auto Xpress [Auto, Enabled, Disabled]

Про эту опцию можно сказать следующее:

Уже в случае с AMD 790X, впрочем, перечень характеристик пополняется за счет Auto Xpress (автоматическое увеличение рабочей частоты шины PCI Express при установке видеокарт AMD на платы с чипсетом AMD; использование специальных режимов работы с DDR2 памятью), GPU-Plex, Quad PCIE Blocks и CrossFireX. Последняя технология особо интересна тем, что отныне в режиме CrossFire могут быть объединены три или даже четыре графических адаптера AMD. Перечень CrossFireX-совместимых видеокарт на данный момент состоит из решений AMD поколения Radeon HD 3800. При производстве новых чипсетов компании был использован 65 нм техпроцесс. Энергопотребление данных наборов системной логики составляет 10-12 Вт (TDP).

Будучи объединенными вместе, все вышеперечисленные компоненты (процессоры Phenom, чипсеты AMD 7, адаптеры Radeon HD 3800 и технология CrossFireX) составляют новую платформу для «энтузиастов» под названием AMD «Spider».

CPU Tweak [Enabled, Disabled]

В BIOS от Asus так называется TLB-патч для процессоров Phenom.

Bank Interleaving [Auto, Disabled]

Включение этого режима позволяет работать с банками по очереди, то есть получать данные из одного в то время, когда другие заняты. Причем выбор значения 2-Way позволяет чередовать пару банков, а 4-Way – четыре банка (они есть у большинства микросхем DIMM-модулей), а это, конечно, выгоднее.

* В тесте памяти Everest с данной опцией Disabled результат снижается на

2,5% по сравнению с Auto.

Channel Interleaving

* У меня эта опция была в BIOS версии 0801, с которой она и продавалась. После прошивки до последней версии 1102 я ее не обнаружил.

DCT Unganged Mode [Enabled, Disabled]

При установке Disabled чипсет должен работать с памятью частотой до 800МГц. Enabled позволяет включить делитель для памяти 1066МГц. Это можно сделать при установке процессоров Phenom.

Read Delay [0,5-4 memory CLKs]

Это поле определяет задержку от включения DQS ресивера до начала чтения первых данных с клавиатуры, получаемых FIFO.

000b = 0.5 Memory Clocks

001b = 1 Memory Clock

010b = 1.5 Memory Clocks

011b = 2 Memory Clocks

100b = 2.5 Memory Clocks

101b = 3 Memory Clock

110b = 3.5 Memory Clocks

111b = 4 Memory Clocks

Прямая корреляция w/memory’s время ожидания. Чем ниже установка, тем ниже время ожидания.

* Со значением 0,5 комп не стартовал, сброс CMOS. С 1 стартует, но пишет что-то вроде ошибки при проверке DRAM. Нормальный запуск при 1,5. В бенчмарке памяти и кэша Everest прирост по сравнению с настройками по умолчанию: по Read — 1,9%; по Copy — 0,5%; по Latency — уменьшение времени доступа на 2,8 ns. По Write изменений нет.

Memory Clock Tristate C3/ALTVID [Enabled, Disabled]

Позволяет частоте памяти DDR быть в трех состояниях (tristated), когда включен дополнительный режим VID. Этот бит не имеет никакого эффекта если установлен бит DisNbClkRamp (Function 3, Offset 88h).

Power Down Enable [Enabled, Disabled]

Если данный режим активирован, то после ввода включения режима Sleep Mode, главному внутреннему тактовому генератору запрещено передавать сигнал на чип устройства. При этом большая часть связанной схемы может отключена от питания для сохранения энергии.

DCQ Bypass Maximu [0x-14x]

Управляющий контроллер обычно позволяет производить за проход другие операции по порядку, чтобы оптимизировать пропускную способность DRAM. Это поле определяет максимальное количество раз, которое самый старый запрос доступа к памяти в очереди контроллера DRAM может быть отложен перед выполнением, и самый старый запрос доступа к памяти будет выполнен вместо другого.

0000b = Никогда не откладывается; самый старый запрос никогда не откладывается.

0001b = самый старый запрос может быть отложен не больше, чем 1 раз.

1111b = самый старый запрос может быть отложен не больше, чем 15 раз.

* оптимальное значение для быстродействия 4. При этом в тесте памяти Everest наибольшая скорость копирования. На чтение, запись и латентность это значение почти не влияет.

DRAM Timing Configuration

Memory Clock Mode [Auto, Limit, Manual]

Установка в Manual открывает следующую опцию:

Memory Clock Value [400, 533, 667, 800]

Позволяет установить делитель для памяти.

PLL1 Spread Spectrum [Enabled, Disabled]

PLL2 Spread Spectrum [Enabled, Disabled]

Опция Spread Spectrum позволяет сгладить пики и уменьшить интерференцию, а также уменьшить взаимное электромагнитное влияние различных компонентов системной платы друг на друга за счет изменения их частоты в некоторых пределах. Рекомендуется отключить для стабильности системы.

PCI Express Configuration

GFX Dual Slot Configuration [Enabled]

GFX2 Dual Slot Configuration [Disabled]

Peer-to-Peer among GFX/GFX2 [Disabled]

Данные опции определяют сколько и в каком режиме будет работать видеоадаптеров, размещенных в слотах. С такими значениями — будут задействованы платы, подсоединенные к верхним синему и черному слотам в равном состоянии для получения запросов и команд.

GPP Slots Power Limit, W [25]

Ограничение мощности слотов GPP

Port #02 и #12 Features

Gen2 High Speed Mode [Disabled, Software Swith, Autonomus Switch]

* Software Switch, Autonomus Switch — включение данных значений дает небольшой прирост в 3DMark06, по сравнению с Disabled. Между собой у них разницы не заметил.

Link Width [Auto, x1Mode, x2, x4, x8, x16]

режим работы слота.

Slot Power Limit, W [175]

максимальная потребляемая мощность, которая может быть подана через слот (0-250).

Port #11

Настройки синего нижнего слота.

NB-SB Port Features

NB-SB Link ASPM [Disabled, L1]

NP NB-SB VC1 Traffic Support [Disabled, Enabled]

виртуальный канал 1) помогает с асинхронным режимом управлять потоком данных и голоса по IP.

Hyper Transport Configuration

HT Link Tristate [Disabled, CAD/CTL, CAD/CTL/CLK]

Включите вариант с тремя состояниями, чтобы уменьшить потребляемую мощность. По умолчанию нет линий в трех состояниях. Также CAD/CTL или CAD/CTL/CLK линии могут быть в трех состояниях.

UnitID Clumping [Disabled, UnitID 2/3, UnitID B/C, UnitID 2/3&B/C]

Включите для поддержки UnitID clumping, чтобы увеличить число отдельных запросов, поддерживаемых одиночным устройством. Это возможно включит для PCI-Express GFX линии в некоторых конфигурациях. Clumping можно включить, только когда используется более низкий мост номера в пределах каждого ядра PCI-Express GFX.

* Точных указаний нет. Вроде как работает вместе с Isochronous Flow-Control Mode и нужно ставить значение UnitID 2/3&B/C.

2X LCLK Mode

Ничего (опция будет удалена в следующей версии).

Полные настройки BIOS

II. Chipset Features Setup

SDRAM CAS Latency Time (Время задержки SDRAM CAS [Column Address Strobe])

Опции: 2, 3

- Управляет задержкой времени (по периодам синхронизирующих импульсов) которая происходит до момента когда SDRAM начинает выполнять команду считывания (read command) после ее получения. Также определяет значение «цикла таймера» для завершения первой части пакетной передачи. Таким образом, чем меньше время ожидания, тем быстрее происходит транзакция. Однако некоторые SDRAM не в состоянии обеспечить меньшее время ожидания, становятся нестабильными и теряют данные.Таким образом, по возможности устанавливайте Время ожидания (SDRAM CAS Latency Time) в поз.2 для оптимальной производительности, но увеличивайте до 3 если система становится нестабильной.

SDRAM Cycle Time Tras/TrcTras/Trc (время цикла памяти SDRAM)

Опции: 5/6, 6/8

- Эта функция позволяет изменить минимальное количество циклов памяти требуемых для Tras и Trc в SDRAM. Tras означает SDRAM`s Row Active Time (время активности ряда SDRAM ), т.е. период времени в течение которого ряд открыт для переноса данных. Также существует термин Minimum RAS Pulse Width (минимальная длительность импульса RAS ). Trc, с другой стороны, означает SDRAM`s Row Cycle Time (цикл памяти/время цикла ряда SDRAM), т.е. период времени в течение которого завершается полный цикл открытия и обновления ряда (row-open, row-refresh cycle).

Установкой по умолчанию является 6/8, более медленной и стабильной чем 5/6. Однако, 5/6 быстрее сменяет циклы в SDRAM, но может не оставлять ряды открытыми на период времени достаточный для полного завершения транзакции данных. Это особенно справедливо для SDRAM с тактовой частотой свыше 100MHz. Следовательно, следует попробовать 5/6 в целях увеличения производительности SDRAM, но следует увеличить до 6/8 если система становится нестабильной.

SDRAM RAS-to-CAS Delay (Задержка SDRAM RAS-to-CAS)

Опции: 2, 3

- Эта опция позволяет вам вставить задержку между сигналами RAS (Row Address Strobe) и CAS (Column Address Strobe). Это происходит когда что-то записывается, обновляется или считывается в SDRAM. Естественно, что уменьшение задержки улучшает производительность SDRAM, а увеличение, наоборот, ухудшает производительность SDRAM.Таким образом, уменьшайте задержку со значения 3 (default) до 2 для улучшения производительности SDRAM. Однако, если уменьшения задержки возникает проблема со стабильностью, то установите значение обратно на 3.

SDRAM RAS Precharge Time (Время предварительного заряда RAS SDRAM)

Опции: 2, 3

- Эта опция устанавливает количество циклов необходимых, чтобы RAS накопил свой заряд перед обновлением SDRAM. Уменьшение времени предзаряда до 2 улучшает производительность SDRAM, но если эта установка недостаточна для установленного SDRAM, то SDRAM может обновляться некорректно и не сможет удерживать данные. Таким образом, для улучшения производительности SDRAM, устанавливайте SDRAM RAS Precharge Time на 2, но увеличивайте до 3, если уменьшение времени предзаряда вызывает проблемы со стабильностью.

SDRAM Cycle Length (Длина цикла SDRAM)

Опции: 2, 3

- Данная характеристика сходна с SDRAM CAS Latency Time. Управляет задержкой времени (по периодам синхронизирующих импульсов) которая происходит до момента когда SDRAM начинает выполнять команду считывания (read command) после ее получения. Также определяет значение «цикла таймера» для завершения первой части пакетной передачи. Таким образом, чем меньше длина цикла, тем быстрее происходит транзакция. Однако, некоторые SDRAM не в состоянии обеспечить меньшую длину цикла, становясь нестабильными. По возможности устанавливайте SDRAM Cycle Length в поз.2 для оптимальной производительности, но увеличивайте до 3 если система становится нестабильной.

SDRAM Leadoff Command (время доступа к первому элементу пакета данных)

Опции: 3, 4

- Данная опция позволяет вам подстроить значение leadoff time, периода времени требуемого до того как можно будет получить доступ к данным хранимым в SDRAM. В большинстве случаев это время доступа к первому элементу пакета данных. Для оптимальной производительности, для быстрого доступа к SDRAM устанавливайте значение на 3, но увеличивайте его до 4, если система становится нестабильной.

SDRAM Bank Interleave (Чередование банка данных SDRAM)

Опции: 2-Bank, 4-Bank, Disabled

- Данная характеристика позволяет вам установить режим interleave(чередование) интерфейса SDRAM. Чередование позволяет банкам SDRAM чередовать их циклы обновления и доступа. Один банк проходит цикл обновления в то время как другой находится в стадии обращения к нему. Это улучшает производительность SDRAM путем маскирования (masking) времени обновления каждого банка. Более внимательное рассмотрение чередования покажет, что с упорядочиванием циклов обновления всех банков SDRAM проявляется эффект схожий с конвейерным эффектом.

Если в системе 4 банка, то CPU может в идеале посылать один запрос данных к каждому из банков SDRAM последовательными периодами синхроимпульсов (consecutive clock cycles). Это значит, что в первом периоде CPU пошлет один адрес к Bank 0 и затем пошлет следующий адрес к Bank 1 во втором периоде, перед тем как пошлет третий и четвертый адреса к Banks 2 и 3 в третьем и четвертом периодах соответственно. Такая последовательность будет иметь примерно следующий вид:

В результате, данные из всех четырех запросов последовательно поступят от SDRAM без задержек между ними. Но, если чередование не было активизировано, та же самая 4-х адресная транзакция примет следующий вид:

Как видите, с чередованием, первый банк начинает перенос данных к CPU в том же самом цикле при котором второй банк получает адрес от CPU. Без чередования, CPU посылал бы этот адрес к SDRAM, получал бы требуемые данные и затем ждал бы пока обновится SDRAM, перед тем как начать вторую транзакцию данных. На все это тратится множество периодов синхроимпульсов. Вот почему пропускная способность SDRAM увеличивается при включенном чередовании (interleaving enabled).

Однако, чередование банков (bank interleaving) работает только в том случае если последовательно запрошенные адреса не находятся в одном и том же банке. Иначе транзакции данных происходят так, словно эти банки не чередуются. CPU придется подождать пока не очистится первая транзакция данных, а этот банк SDRAM не обновится, и только затем CPU сможет послать еще один запрос к этому банку.

Каждый SDRAM DIMM состоит либо из 2-х банков, либо 4-х банков. Двухбанковые SDRAM DIMM используют 16Mbit SDRAM чипы и обычно бывают 32MB или менее в размере. Четырехбанковые SDRAM DIMM, с другой стороны, обычно используют 64Mbit SDRAM чипы, хотя SDRAM плотность может достигать 256Mbit на один чип. Все SDRAM DIMMs размером хотя бы 64MB или более по природе своей являются 4-банковыми. Если вы используете отдельный 2-bank SDRAM DIMM, то устанавливайте значение этой опции на 2-Bank. Но если вы используете пару 2-bank SDRAM DIMMs, то можно также применить 4-Bank опцию. С 4-bank SDRAM DIMMs, вы можете использовать любую из опций чередования (interleave options).

Размер апертуры AGP устанавливает следующая формула: максимально используемая AGP память x2 плюс 12MB. Это значит что размер используемой памяти AGP составляет менее половины размера апертуры AGP. Это из-за того, что система требует не кэшированную память AGP плюс равное количество области памяти для комбинированной записи и дополнительные 12MB для виртуальной адресации. Это адресное пространство, а не используемая физическая память. Физическая память размещается и высвобождается по необходимости только когда Direct3D запрашивает («create non-local surface») запрос.Win95 (с VGARTD.VXD) и Win98 используют «эффект водопада» («waterfall effect»). Поверхности сначала создаются в локальной памяти. Когда эта память заполнена, процесс создания поверхности вытекает в AGP память и затем в системную память. Таким образом, использование памяти автоматически оптимизируется для каждого приложения. Память AGP и системная память не используются без абсолютно крайней необходимости.

Рекомендуется держать данную функцию включенной (позиция enable) за исключением случаев, когда в системе имеется много медленных PCI устройств. В этом случае отключение данной функции предотвратит генерацию большого количества повторных попыток, которые могут серьезно нагрузить шину PCI.

Master Priority Rotation

Опции: 1 PCI, 2 PCI, 3 PCI

- Данная функция контролирует доступ CPU к шине PCI. Если выберете позицию 1 PCI, CPU всегда будет иметь доступ к текущей шине PCI после того, как будет закончена транзакция независимо от того, сколько других шин PCI находится в очереди. Это обеспечивает моментальный доступ CPU к шине PCI, но означает более медленную работу устройств PCI. Если выбираете позицию 2 PCI, CPU получит доступ после того, как текущая и следующая PCI транзакции будут закончены. Другими словами, CPU получает доступ после двух транзакций PCI, независимо от того, сколько других устройств передачи данных по шине PCI будет в очереди. Это означает, что CPU вынужден будет ждать несколько дольше, чем в предыдущем опции (1 PCI), но устройства PCI получат более быстрый доступ к шине PCI. Если выберете опцию 3 PCI, CPU получит доступ к PCI шине после того, как будут закончены текущая и две последующих транзакции устройствами передачи данных по шине PCI. Таким образом, CPU вынужден будет ждать, пока три устройства передачи данных, находящихся в очереди, не закончат свои транзакции через шину PCI прежде, чем он получит доступ к самой шине PCI. Это означает более медленную коммуникацию от CPU к PCI, но PCI устройства будут работать лучше. Но, независимо от выбора, CPU будет иметь доступ к PCI после максимум 3 транзакций устройствами передачи данных по шине PCI. Это произойдет независимо от того, сколько устройств передачи данных по PCI будет находиться в очереди, или когда CPU запросит доступ к шине PCI. Процессор всегда получит доступ к шине PCI после одной транзакции (1 PCI), двух транзакций (2 PCI) или трех транзакций (3 PCI).

Режим AGP 4X

Опции: Enable, Disabled

- Данная функция имеется только у материнских плат, поддерживающих AGP4X. Однако, она обычно отключена (выбрана позиция Disabled) по умолчанию, так как не каждый использует карту AGP4X. У пользователей карт AGP1X или 2X данная функция BIOS должна быть отключена, чтобы карты смогли нормально работать. Для того, чтобы избежать осложнений, производители предпочитают просто отключать режим AGP4X. Однако, это означает, что пользователи карт AGP4X не смогут воспользоваться большой пропускной способностью, которая доступна в режиме AGP4X. Хотя скорость передачи данных в режиме AGP4X незначительно выше, чем в режиме AGP2X, все равно будет неразумно не воспользоваться возможностями этого режима. Так что, если у вас видеокарта AGP4X, рекомендуется включить режим AGP4X (позиция enable) для лучшей работы шины AGP. Не включайте данный режим, если карта поддерживает только режимы передачи данных AGP1X или AGP2X.

AGP Driving Control

Опции: Автоматический режим, Ручной режим

- Данная функция BIOS позволяет настраивать управление работой порта AGP. Обычно по умолчанию выбирается автоматический режим (позиция Auto), что позволяет чипсету автоматически настраивать работу AGP в соответствии установленной видеокартой формата AGP. Однако для устранения сбоев в работе и «разгона» шины можете перейти в ручной режим управления работой шины AGP для выбора необходимого значения AGP Driving Value.

AGP Driving Value

Опции: от 00 до FF (шестеричная система)

- Данная опция зависит от функции BIOS, которая отвечает за настройку управления AGP (см. выше). Если эта функция будет переведена в автоматический режим, (позиция Auto), то значение, которое вы будет устанавливать в данной опции, работать не будет. Для того чтобы данная опция BIOS работала, необходимо перевести функцию настройки управления AGP в ручной режим (позиция Manual). AGP Driving Value определяет интенсивность сигнала шины AGP. Чем больше значение, тем сильнее сигнал. Диапазон значений в шестеричной системе счисления (от 00 до FF) соответствует диапазону от 0 to 255 в десятичных значениях. По умолчанию значение AGP Driving Value установлено на DA (218), однако, если вы используете AGP карту серии NVIDIA GeForce2, рекомендуется установить AGP Driving Value на более высокое значение EA (234).

Характер данной опции BIOS позволяет «разгонять» шину AGP (работать на большей частоте, чем предусмотрено). Шина AGP чувствительна к «разгону», особенно в режиме AGP4X и с активированной повышенной пропускной способностью. По сути более высокое значение AGP Driving Value может оказаться как раз тем способом для «разгона» шины AGP, который Вам необходим. Увеличением силы сигнала шины Вы можете повысить стабильность ее работы на больших скоростях.Однако, будьте предельно осторожны, увеличивая значение AGP Driving Value при «разогнанной» шине AGP, так как Вы можете безнадежно повредить свою AGP карту! Кстати, вопреки некоторым сообщениям увеличение значения AGP Driving Value не улучшит работу шины AGP. Это не та опция, которая увеличивает производительность шины, так что не следует задирать ее значение, если в этом нет необходимости.

Dram rapl bwlimit что это в биосе

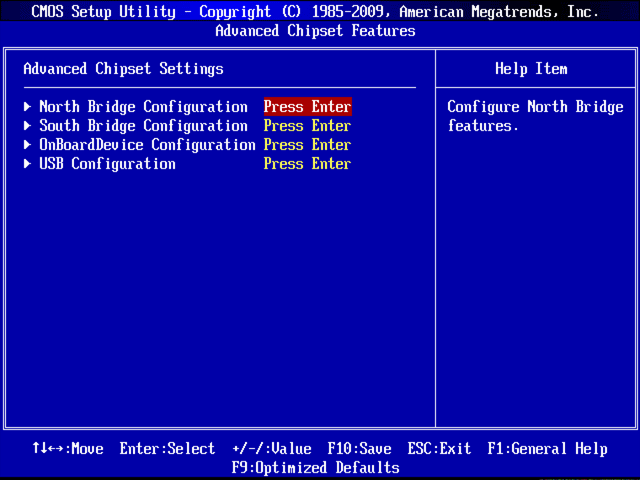

Давайте попробуем произвести настройки северного моста чипсета, который обеспечивает работу быстродействующих компонентов системы: процессора, кэш-памяти, оперативной памяти и видеосистемы. Обычно эти параметры собраны в разделе Advanced Chipset Features, а в версиях BIOS с горизонтальной строкой меню — в меню Advanced или аналогичном.

В некоторых системных платах производства Gigabyte часть настроек чипсета скрыты, и для получения доступа к ним следует нажать клавиши Ctrl+Fl после входа в BIOS Setup.

Оперативная память — один из важнейших компонентов системы, оказывающих заметное влияние на скорость и стабильность работы компьютера. Модули памяти работают по сложным алгоритмам и требуют правильно устанавливать значения рабочих частот и различных временных интервалов. Для обычного (не разогнанного) режима работы системы нет необходимости заниматься наладкой памяти вручную, поскольку в современных модулях памяти все необходимые параметры устанавливаются автоматически. С помощью настройки BIOS вы можете отключить автоматическую наладку и задавать все параметры вручную. При этом можно повысить производительность системы, правда, вам придется взять на себя всю ответственность за стабильность ее работы.

В большинстве компьютеров используется память SDRAM, DDR или DDR2/3. Память стандарта EDO и FPM, выполненная в виде модулей SIMM, является устаревшей и не будем ею засорять себе мозг.

Настройка BIOS, оперативная память, тайминги оперативной памяти.

Оперативная память работает по управляющим сигналам от контроллера памяти, который расположен в северном мосту чипсета (Intel) или непосредственно в процессоре (Athlon 64/FX/X2 и Phenom). Чтобы обратиться к определенной ячейке памяти, контроллер вырабатывает последовательность сигналов с некоторыми задержками между ними. Задержки необходимы, чтобы модуль памяти успел выполнить текущую команду и подготовиться к следующей. Эти задержки называют таймингами и обычно измеряют в тактах шины памяти.

Если тайминги будут слишком большими, то чип памяти выполнит все необходимые действия и будет некоторое время простаивать, ожидая следующую команду. В этом случае память работает медленнее, но стабильнее. Если тайминги излишне маленькие, модуль памяти не сможет корректно выполнить свои задачи, в результате чего произойдет сбой в работе программы или всей операционной системы. Иногда при таких таймингах компьютер может вообще не загрузиться, тогда придется обнулять с помощью перемычки на системной плате.

У каждого модуля памяти свои значения таймингов, при которых производитель гарантирует быструю и стабильную работу памяти. Эти значения записаны в специальном чипе под названием SPD (Serial Presence Detect). Используя информацию SPD, BIOS может автоматически конфигурировать любой модуль памяти из числа тех, которые поддерживаются чипсетом системной платы.

Большинство версий BIOS позволяет отказаться от использования SPD и настроить память вручную. Можно попытаться снизить значения таймингов, чтобы ускорить работу памяти, но после этого следует тщательно протестировать систему.

Для современных модулей памяти SDRAM и DDR выделяют четыре основных тайминга и один параметр работы контроллера памяти. Для понимания их сути кратко рассмотрим работу контроллера памяти.

1. Цикл доступа к определенной ячейке памяти начинается с того, что контроллер устанавливает низкий уровень сигнала выборки строки RAS# (Row Address Strobe) и выставляет адрес строки на линиях адреса. При поступлении этой команды модуль памяти начинает процесс открытия строки, адрес которой был передан по адресным линиям.

2. Через определенный промежуток времени, необходимый, чтобы открыть выбранную строку, контроллер памяти устанавливает низкий уровень сигнала выборки столбца CAS# (Column Address Strobe). На линиях адреса уже будет установлен адрес столбца, который нужно открыть.

3. Через некоторое время после подачи сигнала CAS# модуль памяти начнет передачу запрошенных данных.

4. Для закрытия строки контроллер памяти отключает сигналы RAS# и CAS#, установив на соответствующих выводах высокий уровень. После этого начинается подзарядка закрываемой строки, но при этом может завершаться передача пакета с данными.

5. Если нужно прочитать данные из другой строки, новый сигнал выборки строки (RAS#) может быть подан только через некоторое время после закрытия предыдущей строки, которое необходимо для подзарядки закрываемой строки.

В соответствии с приведенным выше упрощенным описанием выделяют следующие тайминги (в порядке их значимости):

□ tCL, или CAS# Latency — задержка между подачей сигнала выборки столбца CAS# и началом передачи данных, то есть между этапами 2 и 3;

□ tRCD, или RAS# to CAS# delay — задержка между сигналом выборки строки RAS# и сигналом выборки столбца CAS# (этапы 1 и 2);

□ tRP, или RAS# Precharge — задержка для подзарядки строки после ее закрытия (этапы 4 и 5);

□ tRAS, или Active to Precharge Delay — минимальное время между командами открытия строки и ее закрытия (этапы 1-4);

□ CR, или Command Rate — дополнительный параметр, указывающий количество тактов для передачи команды от контроллера к памяти. Оказывает существенное влияние на производительность современных модулей памяти и может принимать значение 1 или 2 такта.

При указании характеристик модуля памяти тайминга обычно указывают по следующей схеме: tCL-tRCD-tRP-tRAS-CR, например модуль памяти Kingston, 1GB DDR2 РС2-5300 имеет тайминга в штатном режиме 4-4-4-12-1Т. Параметр Command Rate (CR) может не указываться, и тогда тайминги будут записываться последовательностью из четырех чисел (4-4-4-12). Если посчитать количество импульсов тактового генератора между основными этапами работы контроллера, то можно получить схему таймингов 2-3-3-7, что характерно для памяти DDR.

Для справки:

DRAM Timing Selectable, Timing Mode

Это основной параметр для настройки оперативной памяти, с помощью которого выбирается ручной или автоматический режим.

Возможные значения:

1. By SPD (Auto) — параметры модулей памяти устанавливаются автоматически с помощью данных из чипа SPD; это значение по умолчанию, и без особой необходимости менять его не следует;

2. Manual — параметры модулей памяти устанавливаются вручную. При выборе этого значения можно изменять установки рабочих частот и таймингов памяти. Ручная настройка оперативной памяти позволяет ускорить ее работу, но при этом в системе могут быть сбои.

Configure DRAM Timing by SPD, Memory Timing by SPD

Смысл этих параметров полностью аналогичен рассмотренному выше DRAM Timing

Selectable, а возможные значения будут такими:

1. Enabled (On) — параметры оперативной памяти устанавливаются автоматически в соответствии с данными SPD;

2. Disabled (Off) — оперативная память настраивается вручную.

Memory Frequency, DRAM Frequency, Memclock Index Value, Max Memclock

Параметр отображает или устанавливает частоту работы оперативной памяти. Эта частота в большинстве случаев задается автоматически в соответствии с информацией из SPD. Настраивая вручную, можно заставить память ускориться, однако далеко не каждый модуль при этом будет работать стабильно.

Возможные значения:

1. Auto — частота оперативной памяти устанавливается автоматически в соответствии с данными SPD (по умолчанию);

2. 100,120,133 (РС100, РС133) — возможные значения для памяти SDRAM;

3. 200, 266, 333, 400, 533 (DDR266, DDR333, DDR400, DDR533) — возможные значения для памяти DDR;

4. DDR2-400,DDR2-566, DDR2-667, DDR2-800, DDR2-889, DDR2-1067 — значения для памяти DDR2.

В зависимости от используемого чипсета список доступных значений может отличаться от приведенного, в нем будут указаны только те частоты, которые поддерживаются платой.

В некоторых платах рассматриваемый параметр доступен только для чтения, а для изменения частоты памяти следует использовать рассмотренный далее параметр FSB/Memory Ratio. В системных платах производства ASRock для ручной настройки памяти следует отключить параметр Flexibility Option.

FSB/Memory Ratio, System Memory Multiplier

Параметр определяет соотношение (множитель) между частотой FSB и частотой памяти. Данный параметр может использоваться вместо рассмотренного выше параметра Memory Frequency для установки частоты работы оперативной памяти.

Возможные значения:

1. Auto — соотношение между частотой FSB и памяти настраивается автоматически в соответствии с данными SPD;

2. 1:1; 1:1, 2; 1:1, 5; 1:1, 66; 1:2, 3:2; 5:4 — выбор одного из этих значений позволит вручную установить соотношение между частотами FSB и памяти. Для расчета частоты памяти следует учитывать, что частота FSB может указываться с учетом четырехкратного умножения (эффективное значение), а частота DDR — с учетом двукратного. Например, при эффективной частоте FSB 1066 МГц и множителе 1:1,5 результирующая частота памяти будет равна (1066:4) х 1,5 х 2 — 800 МГц. В зависимости от модели платы набор соотношений может несколько отличаться от приведенного выше;

3. 2, 00; 2, 50; 2, 66; 3, 00; 3, 33; 4,00 — при наличии подобного ряда частота памяти вычисляется умножением реальной частоты FSB на выбранный коэффициент;

4. Sync Mode — память работает синхронно с частотой FSB.

CAS# Latency, tCL, DRAM CAS# Latency

Параметр устанавливает задержки между подачей сигнала выборки столбца CAS# и началом передачи данных. Эта задержка необходима, чтобы модуль памяти мог сформировать для передачи содержимое запрошенной ячейки памяти. Ручная установка низких значений CAS# Latency увеличивает скорость работы модуля, то есть разгоняет его.

Возможные значения:

1. 1, 5; 2; 2, 5; 3 — для памяти DDR. Меньшие значения соответствует более быстрой работе памяти, однако не все модули могут работать при таких значениях;

2. 3; 4; 5; 6 — для памяти DDR2. Как и в случае с DDR, ускорение памяти достигается уменьшением значения tCL.

В некоторых версиях BIOS к числовому значению таймингов добавляется единица измерения, например 5Т (5 DRAM Clocks).

tRCD, RAS# to CAS# delay, DRAM RAS-to-CAS Delay

Параметр изменяет время задержки между сигналом выборки строки RAS# и сигналом выборки столбца CAS#. Эта задержка необходима, чтобы модуль памяти успел определить и активизировать требуемую строку. Чем меньше значение tRCD, тем быстрее доступ к ячейке, однако, как и в случае CAS Latency, слишком низкие значения могут привести к нестабильной работе памяти.

Возможные значения — от 1 до 7 тактов. Они определяют время задержки между сигналами CAS# и RAS#. Чем меньше значение tRCD, тем быстрее доступ к ячейке, однако, как и в случае CAS Latency, слишком низкие значения могут привести к нестабильной работе памяти.

Настройка BIOS, tRP, DRAM RAS# Precharge, RAS Precharge, SDRAM RAS Precharge, Row Precharge Time

Параметр задает минимально допустимое время, чтобы подзарядить строку после ее закрытия. Другими словами, он определяет паузу между закрытием одной строки и открытием другой с помощью нового сигнала RAS#. При меньших значениях этого параметра память работает быстрее, но слишком низкие могут привести к нестабильной работе памяти.

Возможные значения — от 1 до 7 тактов. Они означают минимальное время в тактах для подзарядки строки и формирования нового сигнала RAS.

tRAS, Active to Precharge Delay, DRAM RAS# Activate to Precharge, Min RAS# Active Time

Параметр устанавливает минимальное время между командой активизации строки и командой закрытия, то есть такое время, в течение которого строка может быть открыта. Слишком высокое значение этого параметра немного снижает производительность, поскольку на закрытие ячейки тратится лишнее время. Чтобы увеличить производительность, попробуйте установить минимальное значение tRAS или же подберите его экспериментально. По имеющимся из разных источников сведениям, параметр tRAS на общую производительность памяти влияет не очень существенно, а оптимальный вариант зависит от типа чипсета.

Возможные значения — от 3 до 18 тактов. Они определяют требуемое время задержки.

DRAM Command Rate, IT/ 2T Memory Timing

Параметр устанавливает задержку при передаче команд от контроллера к памяти. Возможные значения:

1. 2т (2т Command) — величина задержки равна двум тактам; обычно устанавливается по умолчанию и соответствует меньшей скорости, но большей надежности работы памяти;

2. IT (IT Command) — установка задержки в один такт, иногда это позволяет увеличить скорость оперативной памяти. Возможность нормальной работы памяти при таком значении сильно зависит от чипсета и модуля памяти и требует порой экспериментальной проверки. Не рекомендуется устанавливать 1Т при работе памяти на повышенных тактовых частотах или при одновременном использовании нескольких модулей памяти.

2Т Command

Параметр полностью аналогичен рассмотренному выше DRAM Command Rate, но имеет следующие значения:

1. Auto — задержка команд устанавливается в соответствии с данными SPD;

2. Enabled — установлена задержка в 2 такта;

3. Disabled — установлена задержка в 1 такт.

Дополнительные тайминги памяти

Как уже отмечалось, в некоторых системных платах имеются расширенные возможности для настройки памяти и количество доступных таймингов может достигать десятка, а иногда и двух десятков. Дополнительные тайминги оказывают меньшее влияние на производительность, чем рассмотренные выше основные тайминги, поэтому их в большинстве случаев следует оставить по умолчанию. Если же у вас есть время и желание экспериментировать, вы можете несколько повысить производительность системы памяти с их помощью.

Кратко рассмотрим значение дополнительных таймингов.

□ tRRD (RAS to RAS Delay) — задержка между активизацией строк разных банков.

□ tRC (Row Cycle Time), Row Active Time, Raw Pulse Width — длительность цикла строки памяти. Полный цикл состоит из времени от начала активизации строки до ее закрытия (tRAS) и задержки для формирования нового сигнала RAS# (tRP), то есть tRC = tRAS + tRP.

□ tWR (Write Recovery Time) — задержка между завершением операции записи и началом предзаряда.

□ tWTR (Write to Read Delay) — задержка между завершением операции записи и началом операции чтения.

□ tRTP (Precharge Time) — интервал между командами чтения и предварительного заряда.

□ tREF (Refresh period) — частота обновления памяти. Может устанавливаться в тактах или микросекундах.

□ tRFC (ROW Refresh Cycle Time) — минимальное время между командой обновления строки (Refresh) и командой активизации или другой командой обновления. В некоторых версиях BIOS имеется возможность установки данного тайминга для каждого модуля памяти, а параметры будут называться соответственно Trfс 0/½/3 for DIMM 0/½/3.

Важно:

Неудачное изменение любого из таймингов памяти может привести к нестабильной работе компьютера, поэтому при первом же сбое следует установить тайминги по умолчанию.

Bank Interleave

Параметр задает режим чередования при обращении к банкам памяти. В таком режиме регенерация одного банка выполняется в то же время, когда процессор работает с другим банком. Модули памяти объемом 64 Мбайт и более обычно состоят из четырех банков, и включение этого параметра ускоряет работу памяти.

Возможные значения:

1. Auto — режим чередования настраивается автоматически;

2. 2 Way, 4 Way — одно из этих значений устанавливает двух-или четырехбан- ковый режим чередования; рекомендуется использовать 4 Way как обеспечивающий наибольшую производительность, 2 Way может понадобиться, если в системе только один двухбанковый модуль памяти;

3. Disable — режим чередования отключен, что снизит пропускную способность памяти.

DRAM Burst Length, Burst Length

Параметр устанавливает размер пакета данных при чтении из оперативной памяти.

Возможные значения — 4, 8. Они определяют длину пакета данных. При 8 теоретически должна обеспечиваться большая производительность памяти, но практика показывает, что разница копеечная.