Effective clock что это

Краткое руководство по управлению питанием процессора

Как центральный процессор может сокращать собственное энергопотребление? Основы этого процесса — в статье.

Центральный процессор (CPU) спроектирован на бесконечно долгую работу при определенной нагрузке. Практически никто не проводит вычисления круглые сутки, поэтому большую часть времени он не работает на расчетном максимуме. Тогда какой смысл держать его включенным на полную мощность? Здесь стоит задуматься об управлении питанием процессора. Эта тема включает в себя оперативную память, графические ускорители и так далее, но я собираюсь рассказать только про CPU.

Если вы знаете про C-состояния (C-states), P-состояния (P-states) и то, как процессор переходит между ними, то, возможно, в этой статье вы не увидите ничего нового. Если это не так, продолжайте читать.

Я планировал добавить реальные примеры из ОС Linux, но статья становилась все больше, так что я решил приберечь это для следующей статьи.

Основные источники информации, использованные в этом тексте:

Особенности CPU

Согласно официальной странице продукта, мой процессор поддерживает следующие технологии:

Теперь выясним, что значит каждое из этих определений.

Как снизить энергопотребление процессора во время его работы?

На процессорах для массового использования (мы не берем в расчет вещи, которые возможны при их проектировании) для снижения потребляемой энергии можно реализовать один из сценариев:

Второй вариант требует чуть больше объяснений. Энергопотребление интегральной схемы, которой является процессор, линейно пропорционально тактовой частоте и квадратично напряжению.

Примечание для тех, кто разбирается в цифровой электронике: Pcpu = Pdynamic + Pshort circuit + Pleak. При работающем процессоре Pdynamic является наиболее важной составляющей, именно эта часть зависит линейно от частоты и квадратично от напряжения. Pshort circuit пропорционально частоте, а Pleak — напряжению.

Более того, напряжение и тактовая частота связаны линейной зависимостью.

Высокая производительность требует повышенной тактовой частоты и увеличения напряжения, что еще больше влияет на энергопотребление.

Каков предел энергопотребления процессора?

Это во многом зависит от процессора, но для процессора E3-1245 v5 @ 3.50 ГГц расчетная тепловая мощность (Thermal Design Power, TDP) составляет 80 ватт. Это среднее значение, которое процессор может выдерживать бесконечно долго (Power Limit, PL1 на изображении ниже). Системы охлаждения должны быть рассчитаны на это значение, чтобы быть надежными. Фактическое энергопотребление процессора может быть выше в течение короткого промежутка времени (состояния PL2, PL3, PL4 на изображении ниже). TDP измеряется при нагрузке высокой вычислительной сложности (худший случай), когда все ядра работают на базовой частоте (3.5 ГГц).

Как видно на изображении выше, процессор в состоянии PL2 потребляет больше энергии, чем заявлено в TDP. Процессор может находиться в этом состоянии до 100 секунд, а это достаточно долго.

Состояния питания (C-states) vs состояния производительности (P-states)

Состояния питания (C-states) vs состояния производительности (P-states)

Вот два способа снизить энергопотребление процессора:

P-состояния описывают второй случай. Подсистемы процессора работают, но не требуют максимальной производительности, поэтому напряжение и/или тактовая частота для этой подсистемы может быть снижена. Таким образом, P-состояния, P[X], обозначают, что некоторая подсистема (например, ядро), работает на заданной паре (частота, напряжение).

Так как большинство современных процессоров состоит из нескольких ядер, то С-состояния разделены на С-состояния ядра (Core C-states, CC-states) и на С-состояния процессора (Package C-states, PC-states). Причина появления PC-состояний очень проста. Существуют компоненты с общим доступом (например, общий кэш), которые могут быть отключены только после отключения всех ядер, имеющих доступ к этому компоненту. Однако мы в роли пользователя или программиста не можем взаимодействовать с состояниями пакета напрямую, но можем управлять состояниями отдельных ядер. Таким образом, управляя CC-состояниями, мы косвенно управляем и PC-состояниями.

Состояния нумеруются от нуля по возрастанию, то есть C0, C1… и P0, P1… Большее число обозначает большее энергосбережение. C0 означает, что все компоненты включены. P0 означает максимальную производительность, то есть максимальные тактовую частоту, напряжение и энергопотребление.

С-состояния

Вот базовые С-состояния (определенные в стандарте ACPI).

Примечание: Из-за технологии Intel® Hyper-Threading существуют также С-состояния потоков. Хотя отдельный поток может работать с С-состояниями, изменения в энергопотреблении происходят, только когда ядро входит в нужное состояние. В данной статье тема C-состояний на потоках рассматриваться не будет.

Вот описание состояний из даташита:

Примечание: LLC обозначает Last Level Cache, кэш последнего уровня и обозначает общий L3 кэш процессора.

Визуальное представление состояний:

Источник: Software Impact to Platform Energy-Efficiency White Paper

Последовательность C-состояний простыми словами:

Однако если ядро работает (C0), то единственное состояние, в котором может находиться процессор, — C0. С другой стороны, если ядро полностью выключено (C8), процессор может находиться в C0, если другое ядро работает.

Примечание: Intel Software Developer’s Manual упоминает про суб-C-состояния (sub C-state). Каждое С-состояние состоит из нескольких суб-С-состояний. После изучения исходного кода модуля ядра intel_idle я понял, что состояния C1 и C1E являются состоянием С1 с подтипом 0 и 1 соответственно.

Число подтипов для каждого из восьми С-состояний (0..7) определяется с помощью инструкции CPUID. Для моего процессора утилита cpuid выводит следующую информацию:

Замечание из инструкции Intel: «Состояния C0..C7 для расширения MWAIT — это специфичные для процессора C-состояния, а не ACPI C-состояния». Поэтому не путайте эти состояния с ACPI C-состояниями, они явно связаны и между ними есть соответствие, но это не одно и то же.

Я создал гистограмму, представленную ниже, из исходного кода драйвера intel_idle для моего процессора (модель 0x5e). Подписи горизонтальной оси:

Имя C-состояния: специфичное для процессора состояние: специфичное суб-состояние.

Вертикальная ось обозначает задержку выхода и целевые резидентные значения из исходного кода. Задержка выхода используется для оценки влияния данного состояния в реальном времени (то есть сколько времени потребуется для возвращения в С0 из этого состояния). Целевое резидентное значение обозначает минимальное время, которое ядро должно находиться в данном состоянии, чтобы оправдать энергетические затраты на переход в это состояние и обратно. Обратите внимание на логарифмический масштаб вертикальной оси. Задержки и минимальное время нахождения в состоянии увеличивается экспоненциально с увеличением номера состояния.

Константы задержок выхода и целевых резидентных значении C-состояний в исходном коде intel_idle

Примечание: Хотя состояния С9 и С10 включены в таблицу, они имеют 0 суб-состояний и поэтому не используются в моем процессоре. Остальные процессоры из семейства могут поддерживать эти состояния.

Состояния питания ACPI

Прежде чем говорить про P-состояния, стоит упомянуть про состояния питания ACPI. Это то, что мы, пользователи, знаем, когда используем компьютер. Так называемые глобальные системные состояния (G[Х]) перечислены в таблице ниже.

Источник: ACPI Specification v6.2

Также существует специальное глобальное состояние G1/S4, Non-Volatile Sleep, когда состояние системы сохраняется на энергонезависимое хранилище (например, диск) и затем производится выключение. Это позволяет достичь минимального энергопотребления, как в состоянии Soft Off, но возвращение в состояние G0 возможно без перезагрузки. Оно более известно как гибернация.

Существует несколько состояний сна (Sx). Всего таких состояний шесть, включая S0 — отсутствие сна. Состояния S1-S4 используются в G1, а S5, Soft Off, используется в G2. Краткий обзор:

Вот поддерживаемые состояния ACPI.

Комбинации состояний ACPI G/S и С-состояний процессора

Приятно видеть все комбинации в таблице:

В состоянии G0/S0/C8 системы процессора запущены, но все ядра отключены.

В G1 (S3 или S4) некорректно говорить про С-состояния (это касается как CC-состояний, так и PC-состояний), так как процессор полностью обесточен.

Для G3 не существует S-состояний. Система не спит, она физически отключена и не может проснуться. Ей необходимо сначала получить питание.

Как программно запросить переход в энергосберегающее С-состояние?

Современный (но не единственный) способ запросить переход в энергосберегающее состояние — это использовать инструкцию MWAIT или инструкцию HLT. Это инструкции привилегированного уровня, и они не могут быть выполнены пользовательскими программами.

Инструкция MWAIT (Monitor Wait) заставляет процессор перейти в оптимизированное состояние (C-состояние) до тех пор, пока по указанному (с помощью другой инструкции, MONITOR) адресу не будет произведена запись. Для управления питанием MWAIT работает с регистром EAX. Биты 4-7 используются для указания целевого С-состояния, а биты 0-3 указывают суб-состояние.

Примечание: Я думаю, что на данный момент только AMD обладает инструкциями MONITORX/MWAITX, которые, помимо мониторинга записи по адресу, работают с таймером. Это еще называется Timed MWAIT.

Инструкция HLT (halt) останавливает выполнение, и ядро переходит в состояние HALT до тех пор, пока не произойдет прерывание. Это означает, что ядро переходит в состояние C1 или C1E.

Что вынуждает ядро входить в определенное С-состояние?

Как отмечалось ранее, переходы между глубокими С-состояниями имеют высокие задержки и высокие энергетические затраты. Таким образом, такие переходы должны выполняться с осторожностью, особенно на устройствах, работающих от аккумуляторов.

Возможно ли отключить С-состояния (всегда использовать С0)?

Это возможно, но не рекомендуется. В даташите (секция 4.2.2, страница 64) есть примечание: «Долгосрочная надежность не гарантируется, если все энергосберегающие состояния простоя не включены». Поэтому вам не стоит отключать С-состояния.

Как прерывания влияют на процессор\ядро в состоянии сна?

Когда происходит прерывание, соответствующее ядро пробуждается и переходит в состояние С0. Однако, например Intel® Xeon® E3-1200 v5, поддерживает технологию Power Aware Interrupt Routing (PAIR), у которой есть два достоинства:

P-состояния

P-состояния подразумевают, что ядро в состоянии С0, потому что ему требуется питание, чтобы выполнять инструкции. P-состояния позволяют изменять напряжение и частоту ядра (другими словами рабочий режим), чтобы снизить энергопотребление. Существует набор P-состояний, каждое из которых соответствует разных рабочим режимам (пары напряжение-частота). Наиболее высокий рабочий режим (P0) предоставляет максимальную производительность.

Процессор Intel® Xeon® E3–1200 v5 позволяет контролировать P-состояния из операционной системы (Intel® SpeedStep Technology) или оставить это оборудованию (Intel® Speed Shift Technology). Вся информация ниже специфична для семейства Intel® Xeon® E3-1200 v5, но я полагаю, это в той или иной степени актуально и для других современных процессоров.

P-состояния, управляемые операционной системой

В этом случае операционная система знает о P-состояниях и конкретном состоянии, запрошенным ОС. Проще говоря, операционная система выбирает рабочую частоту, а напряжение подбирается процессором в зависимости от частоты и других факторов. После того, как P-состояние запрошено записью в моделезависимый регистр (подразумевается запись 16 бит в регистр IA32_PERF_CTL), напряжение изменяется до автоматически вычисленного значения и тактовый генератор переключается на заданную частоту. Все ядра имеют одно общее P-состояние, поэтому невозможно установить P-состояние эксклюзивно для одного ядра. Текущее P-состояние (рабочий режим) можно узнать, прочитав информацию из другого моделезависимого регистра — IA32_PERF_STATUS.

Смена P-состояния мгновенна, поэтому в секунду можно выполнять множество переходов. Это отличает от переходов C, которые выполняются дольше и требуют энергетических затрат.

P-состояния, управляемые оборудованием

В этом случае ОС знает об аппаратной поддержке P-состояний и отправляет запросы с указанием нагрузки. В запросах не указывается конкретное P-состояние или частота. На основе информации от ОС, а также других факторов и ограничений оборудование выбирает подходящее P-состояние.

Я хочу рассказать об этом подробнее в следующей статье, но сейчас я поделюсь с вами своими мыслями. Мой домашний компьютер работает в этом режиме, я узнал это, проверив IA32_PM_ENABLE. Максимальный (но не гарантированный) уровень производительности — 39, минимальный — 1. Можно предположить, что существует 39 P-состояний. На данный момент уровень 39 установлен ОС как минимальный и как максимальный, потому что я отключил динамическое изменение частоты процессора в ядре.

Заметки про Intel® Turbo Boost

Поскольку TDP (расчетная тепловая мощность) — это максимальная мощность, которую процессор может выдержать, то процессор может повышать свою частоту выше базовой, при условии что энергопотребление не превысит TDP. Технология Turbo Boost может временно повышать энергопотребление до границы PL2 (Power Limit 2) на короткий промежуток времени. Поведение Turbo Boost может быть изменено через подсказки оборудованию.

Применима ли эта информация о C-состояниях и P-состояниях к мобильным и встраиваемым процессорам?

Для примера, недавний MacBook Air с процессором i5-5350U в основном поддерживает возможности, описанные выше (но я не уверен про P-состояния, контролируемые оборудованием). Я также смотрел документацию ARM Cortex-A, и, хотя там применяются другие термины, механизмы управления питанием выглядят похоже.

Как это все работает, например, на Linux?

На этот вопрос я отвечу в другой статье.

Как я могу узнать состояние процессора?

Существует не так много приложений, которые могут выводить эту информацию. Но вы можете использовать, например, CoreFreq.

Вот какую информацию можно получить (это не весь вывод).

Вот информация о ядре, включая информацию о драйвере idle.

Мониторинг счетчиков С-состояний (для ядра):

Функции управления производительностью и энергопотреблением процессоров Intel

Мы продолжаем начатое нами исследование технологий управления производительностью и энергопотреблением современных процессоров, начало которому положили наши статьи, посвященные исследованию указанных технологий в процессорах Intel Pentium 4 и Intel Pentium M. Вполне естественно расширить это рассмотрение на случай новых процессоров Intel, основанных на микроархитектуре Intel Core. Примером такого процессора выступит новейший, только что анонсированный «экстремальный» процессор Intel Core 2 Extreme QX6700, характеризующийся четырехъядерной (2×2) конфигурацией процессорного ядра, получившего кодовое наименование Kentsfield.

Конфигурация тестового стенда

Программное обеспечение

Intel Core 2: новые технологии и особенности их реализации

Прежде всего, остановимся на кратком рассмотрении новых технологий управления производительностью и энергопотреблением, реализованных в процессорах семейства Intel Core 2, а также особенностей их реализации, связанных с многоядерной конфигурацией данных процессоров.

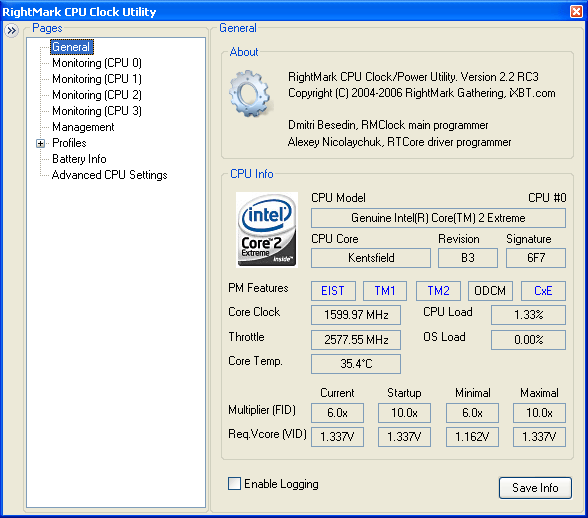

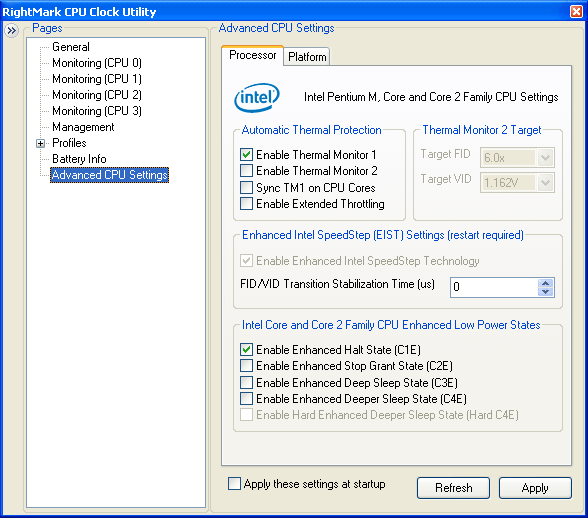

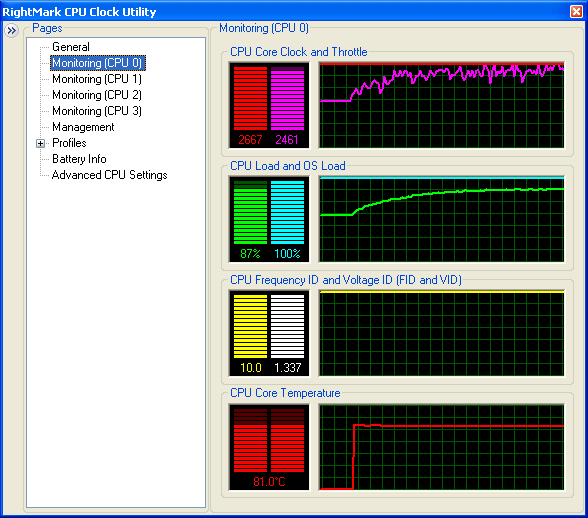

Для начала, взглянем на скриншот последней версии утилиты RightMark CPU Clock Utility 2.2RC3 (pre-release), в которой полностью реализована поддержка двух- и четырехъядерных процессоров семейства Intel Core 2.

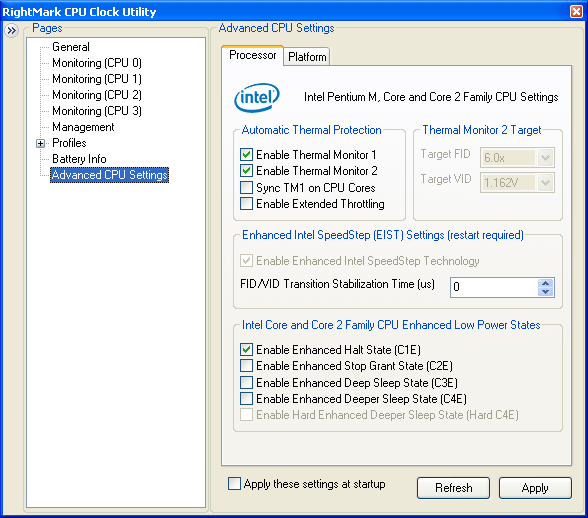

По основному скриншоту видно, что четырехъядерный процессор Intel Core 2 Extreme (Kentsfield) поддерживает все пять рассмотренных ранее технологий управления производительностью и энергопотреблением — технологию управления производительностью процессора по запросу Enhanced Intel SpeedStep (EIST), функции защиты процессора от перегрева Thermal Monitor 1 (TM1) и Thermal Monitor 2 (TM2), устаревшую технологию модуляции тактовой частоты процессора по запросу On-Demand Clock Modulation (ODCM), а также улучшенные режимы простоя Enhanced C States (CxE). По сравнению с процессорами Intel Pentium 4 и Pentium D 600-х, 800-х и 900-х серий, которые, как известно, характеризовались лишь наличием улучшенного режима простоя Enhanced Halt (C1) State, в процессорах Intel Core 2 (а также мобильных процессорах Intel Core Solo/Duo) последняя функция была расширена на случай всех возможных состояний бездействия процессора, включая режимы Stop Grant (C2), Deep Sleep (C3) и Deeper Sleep (C4).

Существенным отличием процессоров семейства Intel Core 2 от рассмотренных нами ранее процессоров Intel является наличие цифровых измерителей температуры ядра (Digital Thermal Sensor), встроенных в каждое ядро процессора. Эти датчики доступны также в мобильных процессорах Intel Core Solo/Core Duo. Их показания можно считывать и отображать независимо для каждого из ядер, что реализовано в последних версиях утилиты RMClock. С технической точки зрения, возвращаемым значением является отрицательное смещение температуры относительно максимально допустимой температуры функционирования ядра процессора (junction temperature, Tj). Последняя указывается в спецификации процессора и составляет 100°C как для процессоров Intel Core Solo/Core Duo, так и для процессоров семейства Intel Core 2. Однако, как показывает опыт, в последнем случае из показаний температуры необходимо вычитать дополнительное смещение, задаваемое в одном из дополнительных модель-специфичных регистров (MSR) процессора, относящихся к рассматриваемым функциям. Это смещение составляет, как правило, 16°C, и его учет реализован в готовящейся к выпуску версии 2.2 утилиты RMClock.

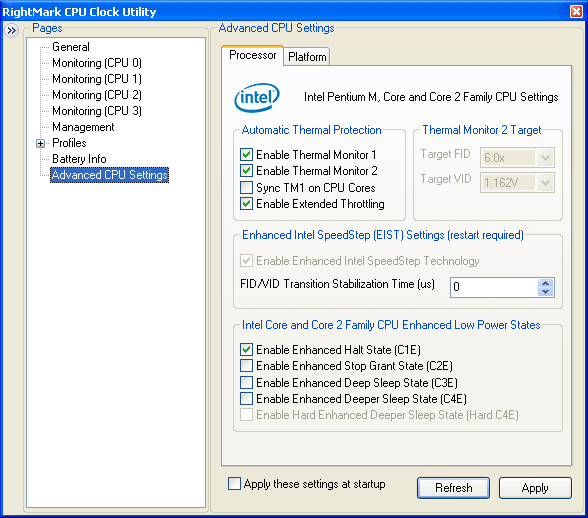

Возвращаясь к улучшенным режимам простоя процессора, из скриншота дополнительных настроек процессора видно, что для десктопных процессоров Intel Core 2 по умолчанию включен лишь режим Enhanced Halt (C1) State — C1E. Связано это с тем, что более глубокие режимы «сна» процессора, как правило, не используются в десктопных платформах — операционная система «не видит» их наличие в информации, предоставляемой ей ACPI BIOS материнской платы. Они приобретают актуальность для мобильных платформ — так, в частности, на платформе Intel Centrino Duo по умолчанию, как правило, оказываются включенными улучшенные режимы C2E и C4E.

Что касается технологий TM1 и TM2, по приведенному скриншоту можно легко увидеть основное отличие в их реализации по сравнению с предыдущими процессорами Intel — в процессорах Intel Core 2 можно задействовать обе технологии одновременно, что в рассматриваемом случае сделано по умолчанию. Однако, как будет показано ниже, само по себе это особого смысла не имеет — для реализации возможности одновременного использования TM1 и TM2 необходимо включение режима так называемого «расширенного троттлинга» (Extended Throttling). Суть последнего, как мы увидим ниже, заключается в аварийном включении технологии TM1 в том случае, если технология TM2 оказывается недостаточно эффективной для сохранения температуры процессора в допустимом интервале температур, заданных производителем. Несмотря на известную высокую эффективность технологии TM2, такая ситуация, в чем легко убедиться, вполне может возникнуть на четырехъядерных процессорах Intel Core 2 Quad / Intel Core 2 Extreme, поэтому мы можем сказать, что режим расширенного троттлинга для этих процессоров предусмотрен производителем явно не зря.

Последняя из дополнительных настроек, являющаяся отключенной по умолчанию, — режим синхронизации TM1 на ядрах процессора (Sync TM1 on CPU cores) — заключается в использовании одного и того же режима модуляции тактовой частоты процессора одновременно для всех его ядер. По всей видимости, особого смысла в использовании этого режима действительно не имеется — ведь каждому из ядер процессора (даже включая те, которые являются составной частью «общего ядра») позволительно иметь собственный режим модуляции тактовой частоты, в зависимости от условий его загрузки и рабочей температуры. С одной стороны, принудительная синхронизация режима TM1 может способствовать более эффективному снижению температуры процессорного ядра в целом, но с другой стороны, она может приводить к более выраженному снижению производительности процессора в случае его перегрева. Видимо, производитель счел более важным сохранение как можно более высокой производительности процессора даже при его сильном перегреве, в связи с чем этот режим не используется по умолчанию.

Говоря о независимости или, наоборот, зависимости отдельных ядер друг от друга, мы перешли к рассмотрению особенностей реализации функций управления производительностью и энергопотреблением процессоров семейства Intel Core 2, поскольку указанные особенности связаны именно с этим обстоятельством. Как известно, классические двухъядерные процессоры Intel Core 2, а также Intel Core Duo, характеризуются наличием общего для обоих ядер процессора L2-кэша. Поскольку этот ресурс функционирует на полной частоте ядра процессора, становится совершенно очевидно, что оба ядра двухъядерных процессоров Intel Core 2 (и Intel Core Duo) всегда обязаны функционировать на одной и той же тактовой частоте. Несмотря на то, что каждое из ядер имеет свой собственный набор модель-специфичных регистров (MSR-ов), предоставляющих возможность управления производительностью и энергопотреблением ядра процессора, попытка установки разных значений тактовой частоты (точнее, множителя системной шины, FID) для разных ядер процессора приводит к немедленному зависанию системы.

Поскольку прямое отношение к тактовой частоте ядра процессора имеют лишь технологии EIST и TM2, одинаковыми для обоих ядер должны быть значения именно этих параметров. А если учесть, что программирование режима TM2 для процессоров Intel Core 2 оказывается недоступным (соответствующий MSR у этих процессоров является «read-only»), проблема синхронизации тактовой частоты ядер сводится к ее управлению посредством технологии EIST. Естественно, драйвер процессора или утилиты управления вроде RMClock должны быть «в курсе» этой особенности управления производительностью двухъядерных процессоров Intel посредством технологии EIST. В то же время, как мы уже упоминали выше, каждому из ядер позволительно иметь собственный уровень «троттлинга» (модуляции тактовой частоты — по запросу, посредством ODCM, либо автоматически, посредством TM1), поскольку «троттлинг» затрагивает лишь исполнительные ресурсы ядра процессора, но не влияет на функционирование его L2-кэша.

На первый взгляд, несколько более сложной может оказаться ситуация управления производительностью и энергопотреблением четырехъядерных процессоров, примером которого является рассматриваемый нами Intel Core 2 Extreme QX6700. Однако таковой она кажется лишь на первый взгляд — дело в том, что ядро этого процессора, по сути, представляет собой как бы два независимых процессора Intel Core 2 Duo E6700, помещенных вместе в один корпус. Соответственно, управление каждым из этих независимых «двухъядерных ядер» оказывается также независимым.

Рассматриваемый процессор представляется операционной системе в виде четырех «системных» процессоров, под которыми, как мы знаем, может подразумеваться все, что угодно — либо полноценное процессорное ядро (например, Intel Pentium M), либо его составная часть (Intel Core Duo или Intel Core 2), либо и вовсе логический процессор (Intel Pentium 4 с технологией Hyper-Threading). Соответственно, для управления каждым из «системных» процессоров необходимо как-либо отнести его к конкретному физическому устройству, а далее — сгруппировать «системные» процессоры по критерию их принадлежности к данному физическому процессору/ядру, которым можно управлять как целым устройством. Для решения этой задачи отлично подходит так называемый APIC ID процессора, который, вообще говоря, может произвольно назначаться ему операционной системой. В случае четырехъядерных процессоров Intel Core 2 младший бит APIC ID означает индекс «зависимого» («дочернего») ядра процессора внутри составляющего его «независимого» («главного») ядра (0 либо 1), а следующий за ним бит APIC ID, смещенный вправо на единицу, отражает индекс «независимого ядра» внутри корпуса процессора. Более наглядно это представлено ниже в таблице.

| Индекс системного процессора | APIC ID | Индекс «главного» ядра, APIC ID[1] >> 1 | Индекс «дочернего» ядра, APIC ID[0] |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 2 | 1 | 0 |

| 2 | 1 | 0 | 1 |

| 3 | 3 | 1 | 1 |

Из этой таблицы видно, что APIC ID процессора не обязательно совпадает с номером связанного с ним «системного» процессора, поэтому полагаться на этот номер было бы ошибочно. Заметим также, что представленная выше расстановка ядер процессора Intel Core 2 Extreme QX6700 формально совпадает с таковой для предыдущих «экстремальных» двухъядерных процессоров, оснащенных технологией Hyper-Threading — например, Intel Pentium Extreme 965. Разница заключается лишь в том, что индексу «главного» ядра в том случае соответствует собственно индекс ядра, а индексу «дочернего» ядра — индекс логического процессора, входящего в состав ядра. Аналогия оказывается более чем полной.

Intel Core 2: тестовые испытания

Выше мы рассмотрели основные технологии управления производительностью и энергопотреблением процессоров семейства Intel Core 2 и особенность их реализации в этих процессорах. Самое время перейти к собственно испытаниям этих технологий.

Поведение технологий EIST и CxE в процессорах Intel Core 2 существенно аналогично их поведению в исследованных нами ранее процессорах Intel Pentium 4 и Intel Pentium M, с точностью до рассмотренных выше особенностей, связанных с многоядерной архитектурой процессоров. Намного больший интерес представляют технологии автоматической защиты процессора от перегрева — TM1 и TM2, получившие развитие в виде расширенного режима троттлинга. Тем более что ситуация перегрева четырехъядерного процессора, как выяснилось, оказывается далеко не такой уж и редкой…

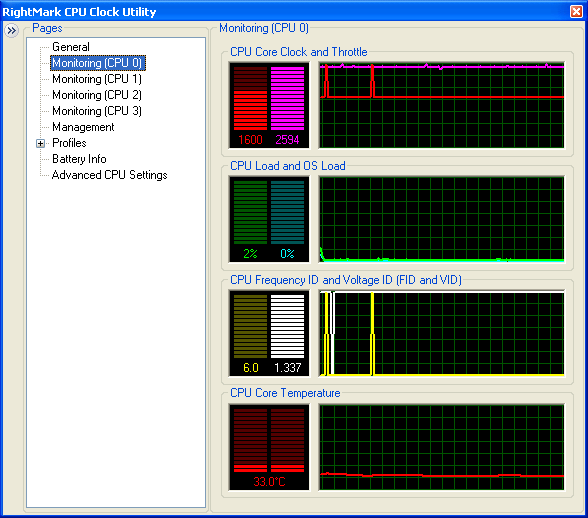

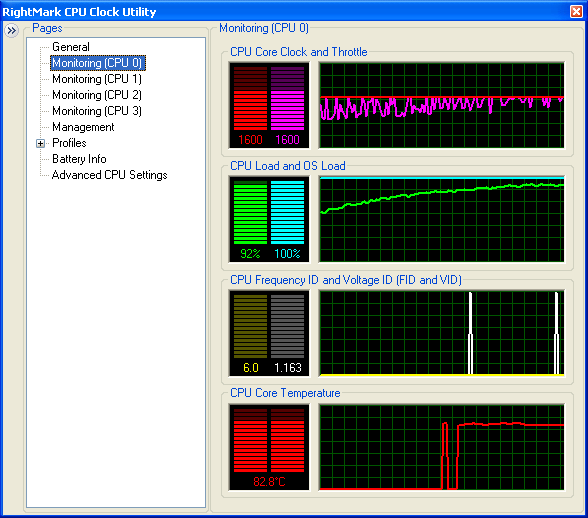

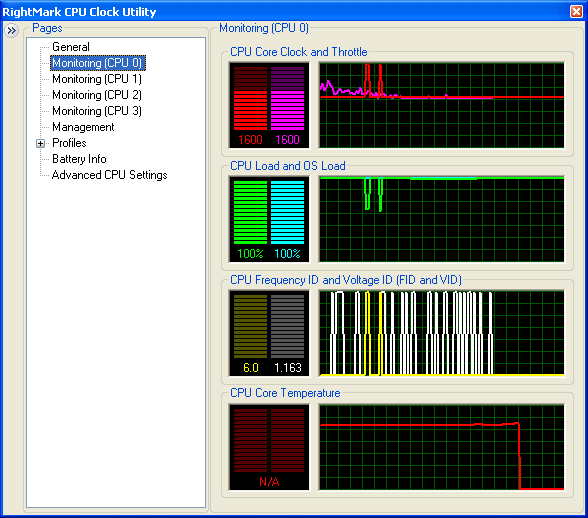

Для начала, рассмотрим вид кривых мониторинга (здесь и далее мониторингу подвергалось первое ядро процессора — «CPU 0», поведение остальных ядер оказывалось в существенной степени аналогичным) в случае простоя процессора.

Видно, что «номинальная» частота ядра процессора оказывается сброшенной до минимального уровня — 1600 МГц (частоты шины 266 МГц, минимальный множитель 6x) за счет функционирования технологий улучшенного режима простоя CxE (в данном случае — C1E). В то же время, измерение «частоты троттлинга» процессора (под которой следует понимать реальную частоту ядра процессора) показывает почти максимальное значение, поскольку само измерение неизбежно является нагрузкой для процессора и выводит его из режима C1E в полностью «рабочее» состояние C0. Температура ядра процессора оказывается на минимальном уровне (порядка 33°C). Следует отметить особенность реализации технологии C1E в процессорах семейства Intel Core 2, заключающуюся в том, что запрашиваемое напряжение ядра процессора (VID), измеряемое при простое системы, как бы практически постоянно остается на максимальном уровне, тогда как множитель системной шины (FID) снижается до минимума. По-видимому, это является особенностью измерения VID на этом типе процессоров, поскольку сама по себе технология C1E по определению помещает процессор в режим минимального энергопотребления, характеризующегося минимальной частотой (FID) и напряжением (VID).

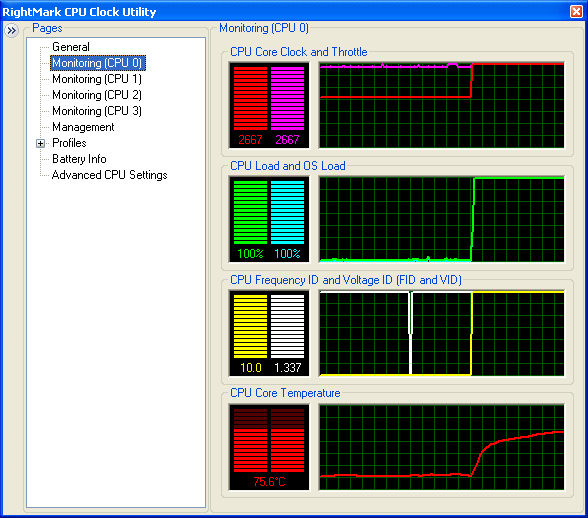

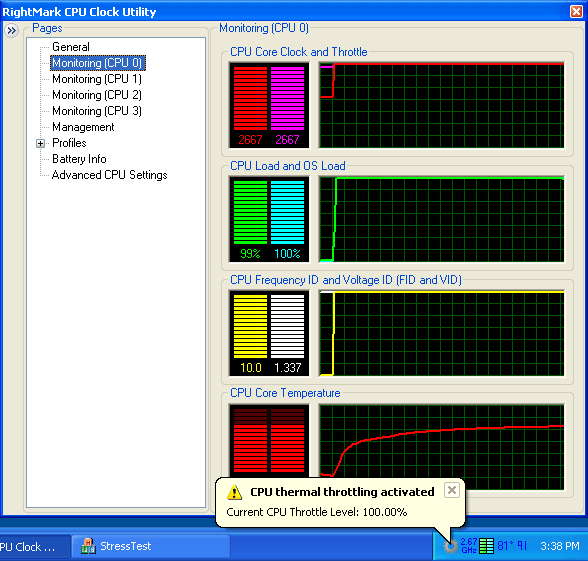

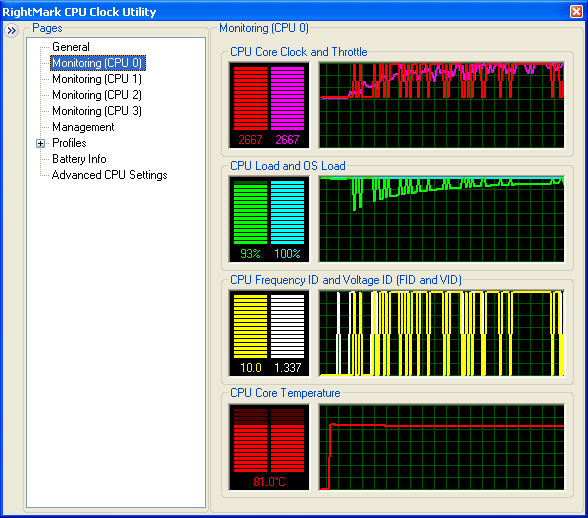

Подаем нагрузку на процессор, моделируемую простым тестовым приложением нашей собственной разработки (StressTest), в данном случае запущенным в четырехпоточном режиме для обеспечения полной загрузки процессора. Частота и загрузка процессора выходят на максимальный уровень, температура ядра очень быстро растет до весьма внушительных величин.

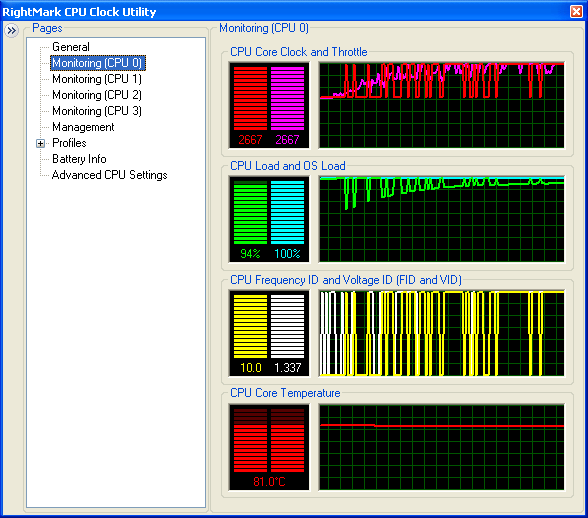

В скором времени, даже в условиях штатной системы охлаждения (надо заметить, весьма шумной!) можно лицезреть картину, представленную на приведенном выше скриншоте. Да-да, все именно так: мы наблюдаем порог срабатывания режима защиты процессора от перегрева. Температура ядра при этом составляет примерно 81°C.

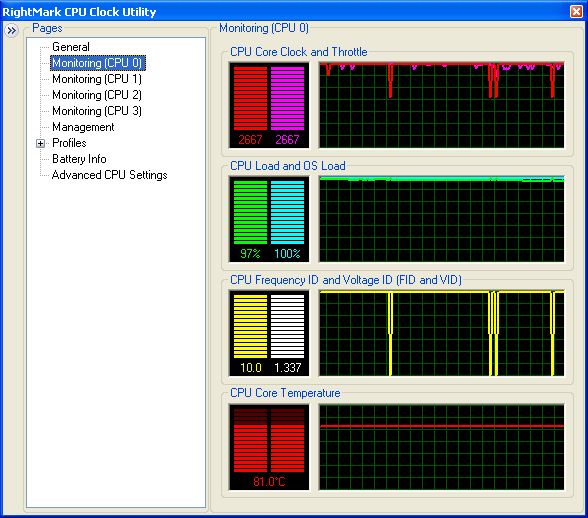

Картина троттлинга в условиях штатного охлаждения разворачивается во времени примерно следующим образом.

На кривых изменения тактовой частоты (а также множителя) процессора во времени легко заметить появление «скачков» до минимального уровня производительности — частоты 1600 МГц при множителе системной шины 6x. Из предыдущих исследований нам хорошо известно, что так работает технология защиты процессора от перегрева TM2. В данном случае (при включенных режимах TM1, TM2, Extended Throttling) она срабатывает в первую очередь, что выглядит вполне естественно, учитывая ее высокую эффективность. Кстати, о последней можно судить также по кривой изменения температуры ядра процессора — она остается на постоянном уровне 81°C. Наконец, по кривой реальной загрузки процессора (CPU Load) можно заметить, что производительность процессора снижается до уровня примерно 97%. Иными словами, хотя троттлинг и имеет место быть (в условиях штатного охлаждения процессора), его влияние на производительность процессора оказывается весьма минимальным.

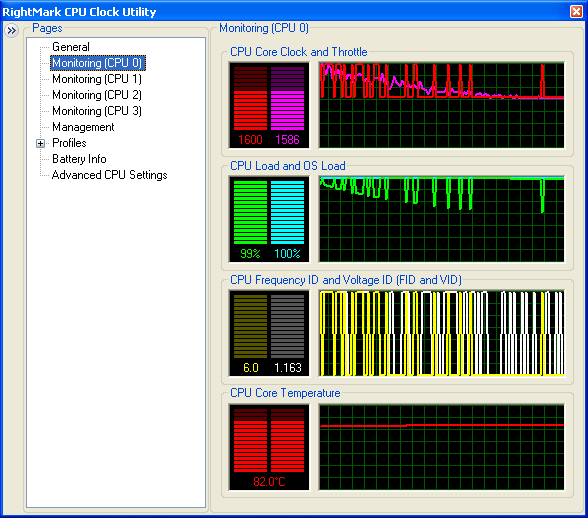

Изучение троттлинга продолжаем следующим образом: с помощью утилиты SpeedFan снижаем скорость вращения вентилятора процессора до минимально возможного уровня. Полная остановка вентилятора нам не удалась, скорость его вращения снизилась примерно до 1000 об/мин.

Достаточно быстро троттлинг процессора посредством TM2 достигает своей максимальной эффективности — «средняя» частота ядра постепенно снижается практически до минимальной отметки, примерно 1.7 ГГц. Это соответствует примерно 64% эффективной производительности ядра процессора, которую, к сожалению, напрямую нельзя увидеть по изменению кривой CPU Load. Дело в том, что последняя отсчитывается относительно текущей, а не «полной» частоты ядра процессора, и в силу ошибок измерения (связанных с множественными переключениями процессора между минимальной и максимальной частотой) она может оказаться даже выше 100%, в том случае, когда реально измеренная «средняя» частота ядра оказывается реально выше по сравнению с синтетическим мгновенным значением «текущей» частоты. Эффективность защиты процессора от перегрева остается на весьма высоком уровне — обратите внимание, насколько мало изменяется температура ядра процессора.

Принципиальных отличий не наблюдается и по мере продолжения испытания. Единственное отличие заключается в том, что «средняя» частота процессора падает до своего минимального значения (в условиях функционирования TM2), равного 1.6 ГГц. Увидеть режим «расширенного троттлинга» не удается в действии даже в этих условиях, при крайне малой скорости вращения вентилятора кулера процессора. Нам ничего не остается, как остановить его полностью, вручную.

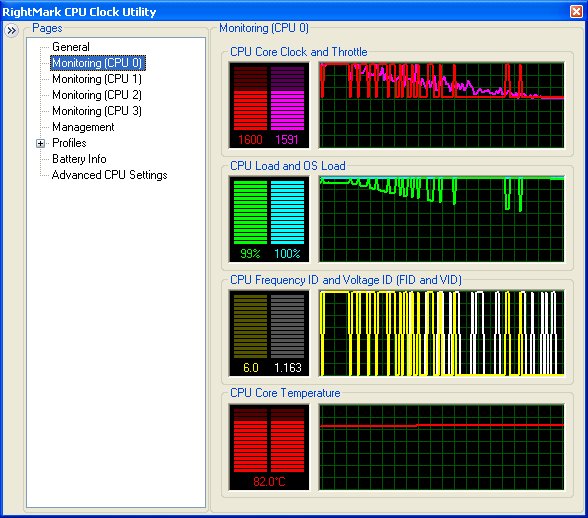

Extended throttling в действии! В реальности все оказалось так, как оно и описано в теории — при недостаточной эффективности TM2 в дело вступает технология TM1, суть которой заключается в модуляции тактовой частоты процессора вставкой «принудительно холостых» тактов. Последняя, измеренная относительно минимальной опорной частоты 1.6 ГГц, в условиях нашего эксперимента достигает отметки примерно 0.91 ГГц, т.е. 57% относительно минимальной частоты процессора, обусловленной действием TM2. По отношению к исходной, полной частоте процессора (2.67 ГГц), эта величина составляет примерно 34%. По-видимому, дальнейшее снижение частоты процессора невозможно даже при одновременном использовании TM2+TM1 в максимальной степени. Обратите внимание на график температуры ядра процессора — в момент экстренного срабатывания TM1 показания последней «исчезают»: цифровой датчик температуры ядра процессора перестает выдавать осмысленные значения, обнуляя при этом свой бит «reading valid», говорящий, как нетрудно догадаться, о корректности выдаваемого им значения. А это означает, что температура ядра процессора отныне не сохраняется на постоянном уровне (примерно 82°C) и продолжает расти. Действительно, устаревшая технология TM1, управляющая лишь эффективной частотой, но не напряжением ядра процессора, неспособна поддерживать его температуру в той же мере, что и технология TM2. По всей видимости, реальная температура ядра в этих крайне жестких условиях испытания продолжает неограниченно расти, пока не достигнет порога срабатывания датчика аварийного перегрева процессора и пока не произойдет принудительное отключение питания системы.

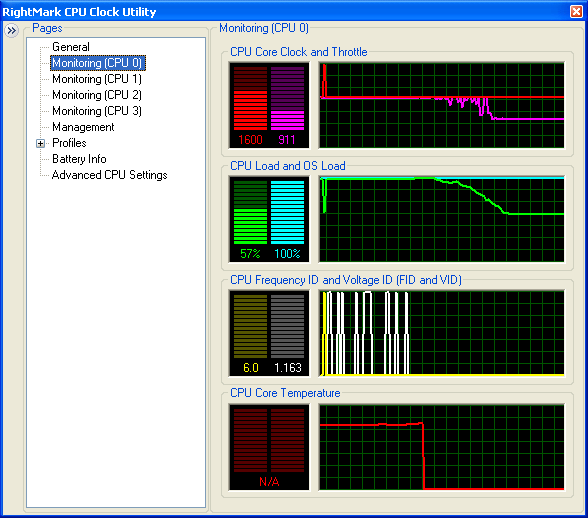

Однако мы не станем дожидаться этого момента, а возобновим активное охлаждение процессора. Сначала вернем установленные программно минимальные обороты вентилятора.

Троттлинг процессора (посредством TM1) весьма медленно сводится на нет, далее появляются первые признаки «оживления» TM2 в виде кратких попыток восстановления максимальной частоты процессора, наконец, возобновляется мониторинг температуры ядра процессора. Следом, возобновляем максимальное охлаждение процессора.

Получаемая картина существенно аналогична картине разворачивания троттлинга процессора посредством TM2, с точностью до обратного порядка следования событий во времени. Постепенно достигается уровень производительности процессора примерно 95%, реально наблюдаемый в условиях полной загрузки последнего при использовании штатной системы охлаждения.

Ради интереса, попробуем теперь отключить режим расширенного троттлинга, оставив при этом одновременно включенными TM1 и TM2. Снизим скорость вращения вентилятора до минимальной.

TM2 достигает своей максимальной эффективности, температура ядра сохраняется на постоянном уровне. Теперь полностью остановим вентилятор кулера процессора.

И увидим границу действия технологии TM2 — сперва исчезают всяческие попытки восстановления максимальной тактовой частоты ядра процессора, а его реальная частота снижается до минимальной. Далее пропадают показания цифрового датчика температуры. Однако, поскольку режим расширенного троттлинга более не используется, технология TM1 при этом не включается.

Восстановление активного охлаждения процессора приводит к возвращению практически максимального уровня производительности процессора.

Напоследок, изучим режим работы устаревшего механизма термической защиты процессора TM1 в чистом виде.

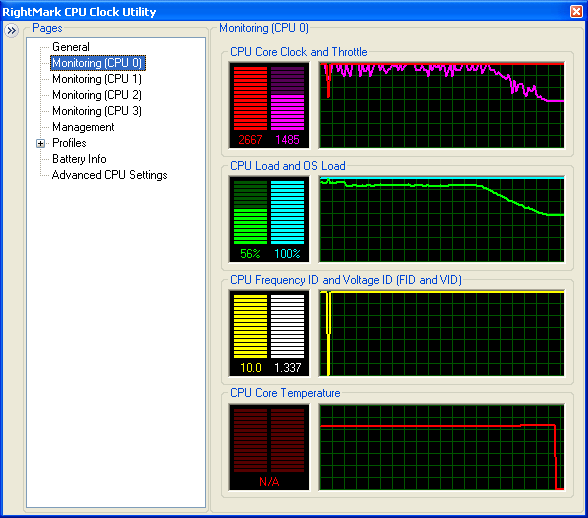

Снижение скорости вращения вентилятора до минимальной оказывается достаточным, чтобы быстро реализовать троттлинг процессора посредством технологии TM1 в полной мере. Опорная частота ядра процессора остается максимальной, однако его реальная частота достаточно быстро снижается до уровня примерно 56% (1.49 ГГц), уже знакомого нам по испытаниям режима расширенного троттлинга. При достижении максимального уровня троттлинга температура ядра процессора достаточно быстро выходит за допустимый предел, в связи с чем показания датчика температуры исчезают. Это лишний раз подтверждает, что технология TM1 оказывается намного менее эффективной по сравнению с TM2. В одинаковых условиях эксперимента эта технология не только приводит к более выраженному снижению частоты процессора, но и оказывается неспособной поддержать его температуру на постоянном уровне.

При возобновлении активного охлаждения процессора температура ядра процессора достаточно быстро возвращается в допустимые рамки, а уровень его производительности достаточно медленно достигает максимального уровня, равного примерно 87% от номинала.

Заключение и практические рекомендации

Проведенные испытания показали недостаточно высокую эффективность штатной системы охлаждения процессора Intel Core 2 Extreme QX6700, которая, к тому же, обладает весьма высоким уровнем шума. В условиях полной загрузки всех четырех ядер процессора штатная система охлаждения не справляется с нагрузкой и приводит к срабатыванию защиты процессора от перегрева посредством троттлинга. Рекомендованным решением этой проблемы является использование более эффективной системы охлаждения. Дополнительные исследования показали, что с этой задачей вполне могут справиться и неэкзотические системы воздушного охлаждения, вроде кулера Zalman CNPS9700NT.

Испытания троттлинга как такового в рассматриваемом процессоре показали весьма высокую эффективность реализации технологии Thermal Monitor 2 в плане поддержания температуры ядра процессора в допустимом пределе в течение длительного времени даже в условиях минимального охлаждения. Однако при возникновении внештатной ситуации, например, при полной остановке вентилятора системы охлаждения процессора в условиях полной загрузки процессора, технология Thermal Monitor 2 может оказаться уже недостаточно эффективной, что приведет к срабатыванию режима расширенного троттлинга — включению технологии Thermal Monitor 1 на фоне Thermal Monitor 2. Наши испытания показали, что в этих условиях температура ядра процессора уже не способна сохраняться в допустимом пределе, что может привести к ее дальнейшему возрастанию и, в конечном счете, к аварийному отключению питания системы. Таким образом, мы считаем, что к проблеме охлаждения четырехъядерных процессоров Intel, каковым является процессор Intel Core 2 Extreme QX6700, следует относиться весьма внимательным образом.