Eventout stm32 что это

Что такое событие STM32 EVENTOUT?

В руководстве к моему STM32 одна из альтернативных функций GPIO (а именно AF15, см. Стр. 138) называется EVENTOUT. Ни в коем случае не определено событие и не дан пример использования.

Какова альтернативная функция EVENTOUT моего STM32?

Проделав некоторые раскопки, нашел это из Технического тренинга STM32F10x V0.3

Генерация сигнала Event Out Генерация

импульса с инструкцией SEV: вывести другой MCU из режима пониженного энергопотребления через его сигнал Event In

Посмотрел инструкцию SEV для дальнейшей информации / подтверждения:

Редактировать анонимно (впоследствии отредактировано для точности и организации) *

SEV это инструкция на ассемблере Некоторые компиляторы C могут разрешить его использование, например, через встроенную сборку __asm__ volatile («sev»); хотя точная форма будет зависеть от компилятора.

При фактическом использовании команда будет выводить импульс в течение одного тактового периода (например, 14 нс с тактовой частотой ядра 72 МГц) на тот вывод, который настроен и активирован через AFIO_EVCR регистр и находится в режиме вывода альтернативной функции.

Было предложено использовать последовательность SEV инструкций и nop для вывода последовательности импульсов с частотой тактовой частоты. Возможно, две последовательные SEV инструкции могут создать более длинный импульс, хотя никаких гарантий против сбоев не упоминалось.

* Комментарий рецензента. Это ответ, представленный в виде правки в ФП анонимным незарегистрированным пользователем. Этот вид редактирования противоречит рекомендациям (слишком радикальным). Исключением для этого редактирования может быть безумие, чтобы не потерять ответ. Ник.

Что такое событие EVENTOUT для STM32?

В руководстве моего STM32, одной из альтернативных функций GPIO (а именно AF15, см. стр. 138) называется EVENTOUT. Ни при каких обстоятельствах не определено событие или заданный прецедент.

Что такое альтернативная функция EVENTOUT моего STM32?

1 ответ

Сделав некоторое копирование, найдите это из STM32F10x технический Обучение V0.3

Генерация сигнала Event Out

Генерация импульсов с инструкцией SEV: пробуждение другого MCU с малой мощности через сигнал Event In

Просмотрел инструкцию SEV для дальнейшего Информация /подтверждение:

Редактировать анонимным (впоследствии отредактированным для точности и организации) *

При фактическом использовании команда выдает импульс в течение одного периода времени (например, 14 нс с частотой ядра 72 МГц) на том, какой штырь сконфигурирован и активирован с помощью AFIO_EVCR и находится в режиме вывода альтернативной функции.

Было высказано предположение, что последовательность команд SEV и nop’s может использоваться для вывода последовательности импульсов на долю часов ставка. Возможно, две последовательные инструкции SEV могут создать более длительный импульс, хотя никаких гарантий от скрещивания не было.

* Комментарий рецензента. Это ответ, представленный как редактирование O.P анонимным незарегистрированным пользователем. Этот вид редактирования противоречит рекомендациям (слишком радикальным). Исключение для этого редактирования может быть безумным, чтобы не потерять ответ. Ник.

Eventout stm32 что это

У каждого из портов ввода/вывода общего назначения (general-purpose I/O port, GPIO) есть четыре 32-битных конфигурационных регистра (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR и GPIOx_PUPDR, здесь x заменяется буквой A, B, C, D, E, F, G, H, I, и у некоторых представителей MCU даже есть порты GPIOJ и GPIOK), два 32-битных регистра данных (GPIOx_IDR и GPIOx_ODR), 32-битный регистр установки/сброса уровня (GPIOx_BSRR), 32-битный регистр блокировки (GPIOx_LCKR) и два 32-битных регистра альтернативных функций GPIO (GPIOx_AFRH и GPIOx_AFRL).

Примечание: информация в этой статье (перевод документации [1]) относится ко всему семейству STM32F4xx, если специально не указано что-то другое.

[Основные функции GPIO]

• До 16 управляемых ножек I/O.

• Состояния выхода: двухтактный драйвер (push-pull) или открытый сток (open drain) с возможностью подключения внутренних верхних (pull-up) и нижних (pull-down) подтягивающих резисторов.

• Поступление данных на выход либо от регистра данных выхода (output data register, GPIOx_ODR), либо от периферийного устройства (альтернативная функция выхода GPIO).

• Выбор скорости переключения выхода для каждой ножки I/O.

• Состояния входа: обрыв или высокое сопротивление (floating), подтяжка вверх (pull-up), подтяжка вниз (pull-up/down), аналоговая функция.

• Входные данные поступают в регистр данных входа (input data register, GPIOx_IDR), или в периферийное устройство (альтернативная функция входа GPIO).

• Регистр установки и сброса бит (GPIOx_BSRR) для побитного доступа на запись в регистр GPIOx_ODR.

• Механизм блокировки (GPIOx_LCKR) предоставляется для заморозки конфигурации I/O.

• Аналоговая функция.

• Регистры выбора альтернативных функций (AF) входа/выхода (до 16 AF на ножку I/O).

• Возможность быстрого переключения, позволяющая менять уровень за каждые 2 периода тактов.

• Гибкое мультиплексирование выводов, позволяющее использовать ножки I/O как GPIO или как аппаратные выводы одного из нескольких внутренних периферийных устройств микроконтроллера.

[Функциональное описание GPIO]

Каждый бит порта GPIO может быть индивидуально сконфигурирован программно для работы в следующих режимах:

• Плавающий вход (высокое входное сопротивление).

• Вход с подтяжкой к плюсу питания (pull-up).

• Вход с подтяжкой к минусу питания (pull-down).

• Аналоговая функция.

• Выход с открытым стоком (open-drain) с верхним нагрузочным резистором (pull-up) или с функцией нижней подтяжки (pull-down).

• Выход с двухтактным драйвером (push-pull), с возможностью верхней или нижней подтяжки.

• Альтернативная функция с двухтактным выходом и с возможностью верхней или нижней подтяжки.

• Альтернативная функция с открытым стоком и с возможностью верхней или нижней подтяжки.

Примечание: подробные физические и электрические характеристики каждого порта I/O следует искать в даташите на конкретную модель микроконтроллера STM32.

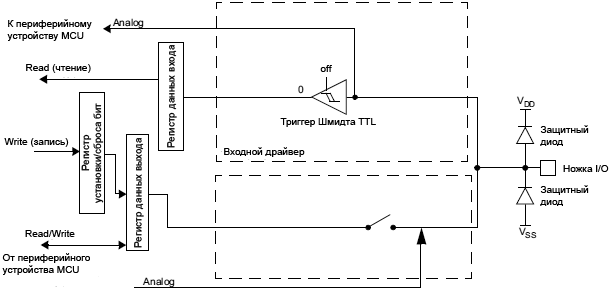

На рис. 25 показана базовая структура бита I/O, который поддерживает возможность подачи на вход уровня 5V (так называемая функция 5V tolerant входа при напряжении питания 3.3V для портов I/O). В таблице 39 представлены возможные конфигурации бита порта.

Рис. 25. Базовая структура 5V-tolerant ножки порта I/O.

Примечание (1): VDD_FT потенциал специфичен для 5V-tolerant I/O и отличается от VDD.

Таблица 35. Конфигурации бита порта (1).

| MODER(i) [1:0] | OTYPER(i) | OSPEEDR(i) [B:A] | PUPDR(i) [1:0] | Конфигурация I/O | |||

| 01 | 0 | SPEED[B:A] | 0 | 0 | GP-выход | PP | |

| 0 | 0 | 1 | GP-выход | PP+PU | |||

| 0 | 1 | 0 | GP-выход | PP+PD | |||

| 0 | 1 | 1 | Зарезервировано | ||||

| 1 | 0 | 0 | GP-выход | OD | |||

| 1 | 0 | 1 | GP-выход | OD+PU | |||

| 1 | 1 | 0 | GP-выход | OD+PD | |||

| 1 | 1 | 1 | Зарезервировано | ||||

| 10 | 0 | 0 | 0 | AF | PP | ||

| 0 | 0 | 1 | AF | PP+PU | |||

| 0 | 1 | 0 | AF | PP+PD | |||

| 0 | 1 | 1 | Зарезервировано | ||||

| 1 | 0 | 0 | AF | OD | |||

| 1 | 0 | 1 | AF | OD+PU | |||

| 1 | 1 | 0 | AF | OD+PD | |||

| 1 | 1 | 1 | Зарезервировано | ||||

| 00 | x | x | x | 0 | 0 | Вход | Плавающий вход |

| x | x | x | 0 | 1 | Вход | PU | |

| x | x | x | 1 | 0 | Вход | PD | |

| x | x | x | 1 | 1 | Зарезервировано (плавающий вход) | ||

| 11 | x | x | x | 0 | 0 | Вход/выход | Analog |

| x | x | x | 0 | 1 | Зарезервировано | ||

| x | x | x | 1 | 0 | |||

| x | x | x | 1 | 1 | |||

Примечание (1): GP = general-purpose, PP = push-pull, PU = pull-up, PD = pull-down, OD = open-drain, AF = alternate function.

GPIO. Во время сброса и непосредственно после него альтернативные функции не активны, и ножки портов I/O конфигурируются в режиме плавающего входа с высоким сопротивлением (input floating mode).

Выводы порта отладки после сброса находятся в альтернативной функции (AF) pull-up/pull-down:

• PA15: вход JTDI с pull-up.

• PA14: вход JTCK/SWCLK с pull-down.

• PA13: вход JTMS/SWDAT с pull-up.

• PB4: вход NJTRST с pull-up.

• PB3: выход JTDO в отключенном состоянии (floating state).

Когда вывод сконфигурирован как выход, записанное значение в регистр выходных данных (GPIOx_ODR) выводится на ножку порта I/O. Можно использовать выходной драйвер ножки порта в режиме двухтактного выхода (push-pull mode) или в режиме открытого стока (open-drain mode, активируется только нижнее плечо N-MOS, когда на выход выводится лог. 0).

Регистр входных данных (GPIOx_IDR) защелкивает в себя данные, присутствующие на ножке I/O, на каждом такте AHB1.

Все ножки GPIO имеют внутренние слабые резисторы подтяжки к плюсу питания (pull-up) и к земле (pull-down), которые могут быть активированы или нет, в зависимости от значения в регистре GPIOx_PUPDR.

Мультиплексирование и отображение ножек I/O. Ножки I/O микроконтроллера подключены ко встроенным периферийным устройствам через мультиплексор, который позволяет в любой момент времени подсоединить в выводу I/O только одну из альтернативных функций (AF). Таким образом не может быть конфликта между разными периферийными устройствами, у которых используется общая ножка порта I/O.

• После сброса все ножки I/O подключены к системной альтернативной функции 0 (AF0), SYS.

• Альтернативные функции периферийных устройств отображаются от AF1 до AF13.

• Cortex®-M4 с FPU EVENTOUT отображается на AF15.

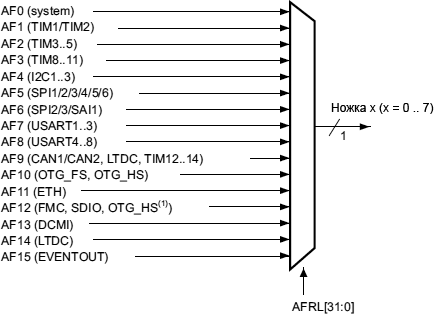

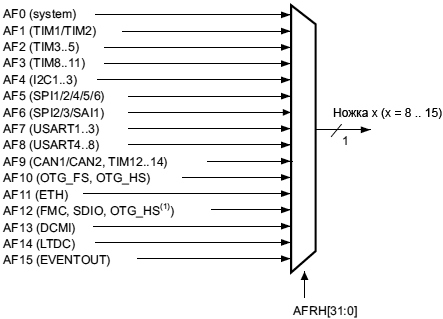

Эта структура показана далее на рисунках 26 и 27.

В дополнение к этой гибкой архитектуре мультиплексирования I/O, каждое периферийное устройство имеет свои альтернативные функции, отображенные на различные ножки I/O, чтобы оптимизировать количество периферийных устройств, доступных в корпусах с меньшим количеством выводов.

Для использования I/O в определенной конфигурации выполните следующие действия:

• Системная функция (SYS). Подключите ножку I/O к AF0 и сконфигурируйте её в зависимости от используемой функции:

– JTAG/SWD, после каждого сброса эти выводы назначаются как выделенные для функции отладки, и могут использоваться хостом отладки (ножка не управляется контроллером GPIO).

– RTC_REFIN: этот вывод должен быть сконфигурирован в режиме входа с высоким сопротивлением (input floating mode).

– MCO1 и MCO2: эти выводы должны быть сконфигурированы в режиме альтернативной функции.

Примечание: пользователь может запретить некоторые или все ножки JTAG/SWD, и таким образом освободить их для использования как GPIO (освобожденные выводы подсвечены серым в таблице 36).

Для дополнительной информации см. секции Section 7.2.10: Clock-out capability и Section 6.2.10: Clock-out capability даташита [1].

• GPIO. Регистром GPIOx_MODER нужная ножка I/O конфигурируется как вход или выход.

• AF (альтернативная функция периферийного устройства). Для ADC и DAC сконфигурируйте нужную ножку I/O как аналоговую с помощью регистра GPIOx_MODER.

Для других периферийных устройств:

– Сконфигурируйте нужную ножку I/O в качестве альтернативной функции с помощью регистра GPIOx_MODER.

– Выберите тип, pull-up/pull-down и скорость переключения выхода соответственно регистрами GPIOx_OTYPER, GPIOx_PUPDR и GPIOx_OSPEEDR.

– Соедините I/O с нужной функцией AFx в регистре GPIOx_AFRL или GPIOx_AFRH.

• EVENTOUT. Сконфигурируйте ножку I/O для вывода Cortex®-M4 сигнала FPU EVENTOUT, путем подключения его к AF15.

Примечание: EVENTOUT не отображается на следующие порты I/O: PC13, PC14, PC15, PH0, PH1 и PI8.

См. таблицу отображения альтернативных функций (Alternate function mapping) в даташите на определенную модель микроконтроллера, где подробно описано отображение каждой ножки порта на альтернативную функцию. Для микроконтроллера STM32F407 таблица альтернативных функций приведена в статье [2], для STM32F429 таблица альтернативных функций приведена в этой статье.

Для ножек от 0 до 7 регистр GPIOx_AFRL[31:0] выбирает выделенную альтернативную функцию:

Для ножек от 8 до 15 регистр GPIOx_AFRH[31:0] выбирает выделенную альтернативную функцию:

Рис. 26. Выбор альтернативной функции на микроконтроллерах STM32F405xx/07xx и STM32F415xx/17xx.

Примечание (1): сконфигурировано в FS.

Для ножек от 0 до 7 регистр GPIOx_AFRL[31:0] выбирает выделенную альтернативную функцию:

Для ножек от 8 до 15 регистр GPIOx_AFRH[31:0] выбирает выделенную альтернативную функцию:

Рис. 27. Выбор альтернативной функции на микроконтроллерах STM32F42xxx и STM32F43xxx.

Примечание (1): сконфигурировано в FS.

Регистры управления портом I/O. Каждый порт GPIO снабжен 32-разрядными, отображенными на адресное пространство памяти регистрами (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR), предназначенными для конфигурирования до 16 ножек I/O.

Регистр GPIOx_MODER используется для выбора направления I/O (ввод, вывод, AF, аналоговая функция). Регистры GPIOx_OTYPER и GPIOx_OSPEEDR используются для выбора типа выхода (push-pull или open-drain) и его скорости переключения (ножки скорости I/O непосредственно подключены к соответствующему регистру GPIOx_OSPEEDR, независимо от направления I/O). Регистр GPIOx_PUPDR используется для выбора подтяжки pull-up/pull-down независимо от направления I/O.

Регистры данных порта I/O. У каждого GPIO есть два 16-битных отображенных на память регистра: регистры входных и выходных данных (GPIOx_IDR и GPIOx_ODR). В GPIOx_ODR сохраняются данные для вывода, он доступен для чтения и записи. Входные данные порта I/O сохраняются в регистре данных входа (GPIOx_IDR), это регистр только для чтения.

Подробное описание регистров данных см. в секции 8.4.5: GPIO port input data register (GPIOx_IDR) (x = A..I/J/K) и секции 8.4.6: GPIO port output data register (GPIOx_ODR) (x = A..I/J/K) даташита [1].

Манипуляция разрядами данных I/O. Регистр установки/сброса бита (GPIOx_BSRR) это 32-битный регистр, позволяющий программе атомарно установить и сбросить отдельный бит в регистре выходных данных (GPIOx_ODR). У регистра установки/сброса GPIOx_BSRR бит в 2 раза больше, чем у регистра выходных данных GPIOx_ODR.

Для каждого бита в GPIOx_ODR соответствуют 2 бита управления в регистре GPIOx_BSRR: BSRR(i) и BSRR(i+SIZE). Когда в бит BSRR(i) записана 1, установится соответствующий бит ODR(i). Когда в бит BSRR(i+SIZE) записана 1, сбросится соответствующий бит ODR(i).

Запись 0 в любой бит регистра GPIOx_BSRR не оказывает никакого влияния на соответствующий бит GPIOx_ODR. Если сделана попытка одновременных установки и сброса бита через регистр GPIOx_BSRR, то действие установки имеет приоритет.

Использование регистра GPIOx_BSRR для изменения значений отдельных бит в GPIOx_ODR работает как «одиночный выстрел», который не блокирует биты GPIOx_ODR. К битам GPIOx_ODR всегда можно обращаться непосредственно. Регистр GPIOx_BSRR предоставляет способ атомарного побитного управления выходными разрядами порта. Таким образом, от программы не требуется запрещать прерывания, когда программируется GPIOx_ODR на уровне бит: есть возможность модифицировать один или большее количество бит за один атомарный доступ на запись по шине AHB1.

Механизм блокировки GPIO. Есть возможность заморозить регистры управления GPIO с помощью выполнения специальной последовательности записи для регистра GPIOx_LCKR. Замораживаются регистры GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR, GPIOx_AFRL и GPIOx_AFRH.

Для записи в GPIOx_LCKR применяется специальная последовательность записи/чтения. Когда правильная последовательность блокировки (LOCK sequence) применена для бита 16 в этом регистре, значение LCKR[15:0] используется для блокировки конфигурации ножек I/O (во время последовательности записи значение LCKR[15:0] должно быть одинаковыми). Когда LOCK sequence применена к биту порта, значение бита порта не может быть модифицировано до следующего сброса MCU или периферии. Каждый бит GPIOx_LCKR freezes the corresponding bit in the control registers (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR, GPIOx_AFRL and GPIOx_AFRH).

LOCK sequence может быть выполнена только доступом к регистру GPIOx_LCKR с использованием 32-битных слов, потому что бит 16 регистра GPIOx_LCKR должен быть установлен одновременно с битами [15:0].

Подробности по функции блокировки см. ниже во врезке с описанием регистра GPIOx_LCKR.

AF (альтернативная функция I/O). Предоставлены 2 регистра для выбора одной из 16 альтернативных функций входа/выхода для каждой ножки I/O. С помощью этих регистров Вы можете подсоединить альтернативную функцию к какой-то другой ножке микроконтроллера, как того требует Ваше приложение.

Это значит, что определенное количество возможных функций периферийных устройств мультиплексируется на каждую ножку GPIO с помощью программирования регистров альтернативных функций GPIOx_AFRL и GPIOx_AFRH. Таким образом, приложение может выбрать одну из возможных функций (AF) для каждой ножки I/O. Сигнал выбора AF общий для альтернативной функции входа и альтернативной функции выхода, один канал выбирается для альтернативной функции ввода/вывода одной ножки I/O.

Чтобы узнать, какие функции мультиплексируются на каком выводе GPIO, см. в даташите на конкретный микроконтроллер таблицу «Alternate function mapping». Для микроконтроллера STM32F407 таблица альтернативных функций приведена в статье [2], для STM32F429 таблица альтернативных функций приведена в этой статье.

Примечание: в любой момент времени для каждой ножки I/O может быть выбрана только одна из альтернативных функций.

Линии сигналов внешнего прерывания/пробуждения. У всех портов есть возможность подачи сигнала внешнего прерывания (external interrupt). Для использования этой функции ножка порта должна быть сконфигурирована в режим входа, см. секции 12.2: External interrupt/event controller (EXTI) и 12.2.3: Wakeup event management в даташите [1].

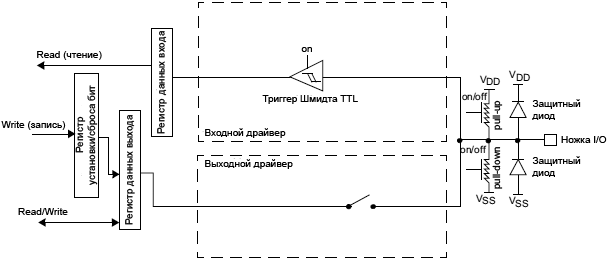

Конфигурация ввода. Когда порт I/O запрограммирован как вход:

• Выходной буфер запрещен.

• Активирован триггер Шмидта по входу.

• В зависимости от записанного значения в регистр GPIOx_PUPDR могут быть активированы верхние (pull-up) и/или нижние (pull-down) резисторы.

• Данные, присутствующие на выводе I/O защелкиваются в регистр входных данных на каждом такте AHB1.

• Доступ на чтение регистра входных данных показывает состояние портов I/O.

Рис. 28 показывает входную конфигурацию бита порта I/O.

Рис. 28. Конфигурации входа для режимов floating, pull-up и pull-down.

Конфигурация вывода. Когда порт I/O запрограммирован как выход:

• Выходной буфер разрешен:

– Режим открытого стока (open-drain): записанный лог. 0 в регистр выходных данных активирует (открывает) нижнее плечо драйвера N-MOS, в то время как записанная лог. 1 переводит ножку порта в отключенное состояние Hi-Z (верхнее плечо драйвера P-MOS никогда не активируется).

– Режим двухтактного выхода (push-pull): записанный лог. 0 в регистр выходных данных активирует (открывает) нижнее плечо драйвера N-MOS, верхнее плечо драйвера P-MOS выключается. Записанная лог. 1 в регистр выходных данных отключает нижнее плечо N-MOS и открывает верхнее плечо P-MOS, на выходе появляется лог. 1.

• Активируется входной триггер Шмидта.

• Активированы ли слабые резисторы подтяжки (weak pull-up и pull-down), или нет, зависит от значения в регистре GPIOx_PUPDR.

• Данные, присутствующие на ножке I/O, защелкиваются в регистр входных данных на каждом такте AHB1.

• Доступ на чтение регистра входных данных показывает состояние портов I/O.

• Доступ на чтение в регистра выходных данных покажет последнее записанное в него значение.

Рис. 29 показывает выходную конфигурацию бита порта I/O.

Рис. 29. Конфигурация выхода.

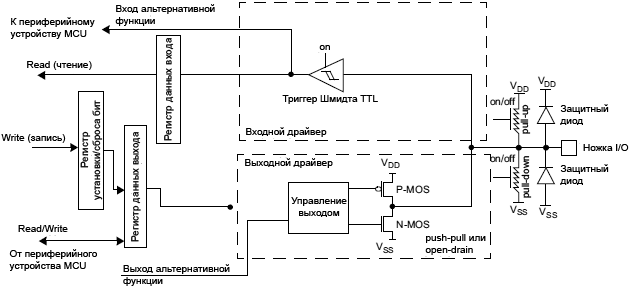

Конфигурация AF. Когда на ножку I/O запрограммирована альтернативная функция (AF):

• Выходной буфер может быть сконфигурирован либо как открытый сток (open-drain), либо как двухтактный буфер (push-pull).

• На выходной буфер поступает сигнал от периферийного устройства (разрешение передатчика и данные от него).

• Активируется входной триггер Шмидта.

• Активированы ли слабые резисторы подтяжки (weak pull-up и pull-down), или нет, зависит от значения в регистре GPIOx_PUPDR.

• Данные, присутствующие на ножке I/O, защелкиваются в регистр входных данных на каждом такте AHB1.

• Доступ на чтение регистра входных данных показывает состояние портов I/O.

Рис. 30 показывает конфигурацию альтернативной функции бита порта I/O.

Рис. 30. Конфигурация альтернативной функции (AF).

Аналоговая конфигурация. Когда ножка порта I/O запрограммирована в analog-режиме:

• Выходной буфер запрещен.

• Триггер Шмидта на входе деактивирован, обеспечивая нулевое потребление тока для каждого аналогового значения на ножке I/O. Выход триггера Шмидта получает постоянное нулевое значение.

• Слабые резисторы подтяжки (weak pull-up и weak pull-down) запрещены.

• Доступ на чтение в регистру входных данных даст значение «0».

Примечание: в analog-конфигурации выводы I/O теряют способность принимать по входу уровень 5V (они не являются 5V tolerant).

На рис. 31 показана высокоомная, аналоговая конфигурация входа для бита порта I/O.

Рис. 31. Hi-Z analog-конфигурация.

OSC32_IN/OSC32_OUT как GPIO. Выводы LSE-генератора OSC32_IN и OSC32_OUT могут использоваться как ножки портов I/O общего назначения, PC14 и PC15 соответственно, когда LSE-генератор выключен. Ножки портов PC14 и PC15 конфигурируются как внешние выводы OSC32_IN и OSC32_OUT только когда LSE-генератор включен. Включение генератора LSE осуществляется установкой бита LSEON в регистре RCC_BDCR. Бит LSE имеет приоритет над функцией GPIO.

Примечание: функционал PC14/PC15 GPIO теряется, когда домен питания 1.2V выключен (когда микроконтроллер входит в режим standby), или когда предоставлен домен питания VBAT (VDD больше не предоставляется). В этом случае I/O установлены в режима аналогового входа.

OSC_IN/OSC_OUT как GPIO. Выводы HSE-генератора OSC_IN и OSC_OUT могут использоваться как ножки портов I/O общего назначения, PH0 и PH1 соответственно, когда HSE-генератор выключен (после сброса HSE-генератор выключен). Ножки портов PH0/PH1 конфигурируются как выводы HSE-генератора OSC_IN/OSC_OUT только когда HSE-генератор включен. Включение HSE-генератора осуществляется установкой бита HSEON в регистре RCC_CR. Функция HSE имеет приоритет над функцией GPIO.

Выбор альтернативных функций RTC_AF1 и RTC_AF2. Микроконтроллер STM32F4xx имеет два вывода GPIO RTC_AF1 и RTC_AF2, которые могут использоваться для детектирования события взлома/вмешательства (tamper event) или события метки времени (time stamp event), или как выходы RTC_ALARM или RTC_CALIB часов реального времени (Real Time Clock, RTC).

RTC_AF1 (PC13) может использоваться для следующих целей:

• Выход RTC_ALARM: этот выход может быть сигналом RTC Alarm A, RTC Alarm B или RTC Wakeup, в зависимости от бит OSEL[1:0] в регистре RTC_CR.

• Выход RTC_CALIB: эта функция разрешается установкой бита COE[23] в регистре RTC_CR.

• RTC_TAMP1: детектирование события взлома (tamper event).

• RTC_TS: детектирование события метки времени (time stamp event).

RTC_AF2 (PI8) может использоваться для следующих целей:

• RTC_TAMP1: детектирование события взлома.

• RTC_TAMP2: детектирование события взлома.

• RTC_TS: детектирование события метки времени.

Выбор соответствующей ножки выполняется через регистр RTC_TAFCR следующим образом:

Механизм выхода следует порядку приоритета, перечисленному в таблицах 37 и 38.

Таблица 37. Ножка RTC_AF1(1).

| Конфигурация и функция ножки | RTC_ALARM разрешено | RTC_CALIB разрешено | Tamper разрешено | Time stamp разрешено | Выбор ножки TAMP1INSEL TAMPER1 | Выбор ножки TSINSEL TIMESTAMP | Конфигурация ALARMOUTTYPE RTC_ALARM |

| Выход Alarm, OD | 1 | Не имеет значения | Не имеет значения | Не имеет значения | Не имеет значения | Не имеет значения | 0 |

| Выход Alarm, PP | 1 | Не имеет значения | Не имеет значения | Не имеет значения | Не имеет значения | Не имеет значения | 1 |

| Выход Calibration, ЗЗ | 0 | 1 | Не имеет значения | Не имеет значения | Не имеет значения | Не имеет значения | Не имеет значения |

| Плавающий вход TAMPER1 | 0 | 0 | 1 | 0 | 0 | Не имеет значения | Не имеет значения |

| Плавающий вход TIMESTAMP и TAMPER1 | 0 | 0 | 1 | 1 | 0 | 0 | Не имеет значения |

| Плавающий вход TIMESTAMP | 0 | 0 | 0 | 1 | Не имеет значения | 0 | Не имеет значения |

| Стандартный GPIO | 0 | 0 | 0 | 0 | Не имеет значения | Не имеет значения | Не имеет значения |

Примечание (1): OD означает open-drain (открытый сток), PP push-pull (двухтактный драйвер).

Таблица 38. Ножка RTC_AF2.

| Конфигурация и функция ножки | Tamper разрешено | Time stamp разрешено | Выбор ножки TAMP1INSEL TAMPER1 | Выбор ножки TSINSEL TIMESTAMP | Конфигурация ALARMOUTTYPE RTC_ALARM |

| Плавающий вход TAMPER1 | 1 | 0 | 1 | Не имеет значения | Не имеет значения |

| Плавающий вход TIMESTAMP и TAMPER1 | 1 | 1 | 1 | 1 | Не имеет значения |

| Плавающий вход TIMESTAMP | 0 | 1 | Не имеет значения | 1 | Не имеет значения |

| Стандартный GPIO | 0 | 0 | Не имеет значения | Не имеет значения | Не имеет значения |

[Регистры GPIO]

В этой секции приведено подробное описание регистров GPIO. Обзорное описание регистров и их бит, вместе с адресами смещения и значениями бит после сброса приведено в таблице 39.

К регистрам GPIO можно обращаться как к байтам (8 бит), половинкам слов (16 бит) или полным словам (32 бита).

В именах регистра x соответствует одной из букв A..I/J/K. Смещения адреса регистра указаны относительно абсолютного адреса, зависящего от буквы. Например, для микроконтроллера STM32F429 эти адреса следующие (данные взяты из заголовочного файла stm32f429xx.h библиотеки CMSIS):

Здесь константа AHB1PERIPH_BASE равна адресу (PERIPH_BASE + 0x00020000UL), или 0x40020000.