Для чего нужно опорное напряжение в ацп

Аналоговые пины

Зачем нужно читать аналоговый сигнал? Микроконтроллер может выступать в роли вольтметра, измерять собственное напряжение питания, например от аккумулятора, может измерять ток через шунт (если вы знаете закон Ома), можно измерять сопротивление, а также работать с потенциометрами (крутильными, линейными, джойстиками), которые являются очень удобными органами управления.

Чтение сигнала

Вот пример, опрашивающий пин А0.

Хранить полученное значение разумно в переменной типа int, потому что значение варьируется от 0 до 1023.

Потенциометры

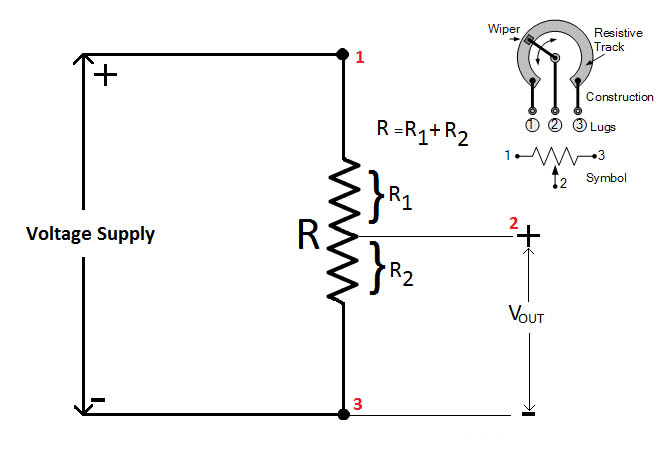

Аналоговые пины и АЦП в целом очень часто используются при работе с потенциометрами (он же переменный резистор или реостат). 10 бит АЦП позволяют дать возможность задавать в программу значения от 0 до 1023 (или кратные им), то есть влиять на ход работы программы, менять какие-то настройки и тому подобное. У потенциометра всегда три ноги: две крайние и одна центральная. Всё вместе это представляет собой делитель напряжения, который и позволяет менять напряжение в диапазоне 0-VCC:

Опорное напряжение

После изменения источника опорного напряжения (вызова analogReference() ) первые несколько измерений могут быть нестабильными (шумными). Значение 1023 функции analogRead() будет соответствовать выбранному опорному напряжению или напряжению выше его, но не выше 5.5V (может повредить плату).

При режиме DEFAULT мы можем оцифровать напряжение от 0 до напряжения питания. Если напряжение питания 4.5 Вольта, и мы подаём 4.5 Вольт – получим оцифрованное значение 1023. Если подаём 5 Вольт – опять же получим 1023, т.к. выше опорного. Это правило работает и дальше, главное не превышать 5.5 Вольт. Как измерять более высокое напряжение, читайте ниже.

Что касается точности: при питании от 5V и режиме DEFAULT мы получим точность измерения напряжения (5 / 1024)

4.9 милливольт. Поставив INTERNAL мы можем измерять напряжение от 0V до 1.1V с точностью (1.1 / 1024)

0.98 милливольт. Весьма неплохо, особенно если баловаться с делителем напряжения. Что касается внешнего источника опорного напряжения.

Нельзя использовать напряжение меньше 0V (отрицательное) или выше 5.5V в качестве внешнего опорного в пин AREF. Также при подключении внешнего опорного напряжения нужно вызвать analogReference(EXTERNAL) до первого вызова функции analogRead() (начиная с запуска программы), иначе можно повредить микроконтроллер! Чтобы “на лету” переключаться между внутренними и внешним опорными, можно подключить его на AREF через резистор на

5 кОм. Вход AREF имеет собственное сопротивление в 32 кОм, поэтому реальное опорное будет вычисляться по формуле REF = V * R * 32 / (R + 32), где R – сопротивление резистора (кОм), через которое подключено опорное напряжение V (Вольт). Например для 2.5V получим 2.5 * 32 / (32 + 5) =

2.2V реальное опорное.

Измерение напряжения

0-5 Вольт

Простой пример, как измерить напряжение на аналоговом пине и перевести его в Вольты. Плата питается от 5V.

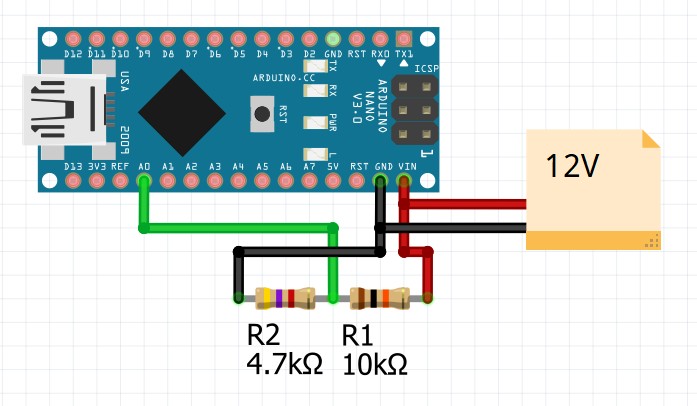

Сильно больше 5 Вольт

Для измерения постоянного напряжения больше 5 Вольт нужно использовать делитель напряжения на резисторах (Википедия). Схема подключения, при которой плата питается от 12V в пин Vin и может измерять напряжение источника (например, аккумулятора):

Как выбрать/рассчитать делитель напряжения?

1 мкА, что в тысячу раз меньше! На самом деле можно взять делитель с гораздо бОльшим суммарным сопротивлением (но не больше 20 МОм, внутреннего сопротивления самого АЦП), но обязательно поставить конденсатор на

Сильно меньше 5 Вольт

Для более точных измерений маленького напряжения можно подключить пин AREF к источнику низкого опорного напряжения (об этом было выше), чтобы “сузить” диапазон работы АЦП. Источник может быть как внешний, так и внутренний, например изменив опорное на внутреннее 1.1V ( analogReference(INTERNAL) ) можно измерять напряжение от 0 до 1.1 Вольта с точностью 1.1/1024

Видео

Аналого-цифровое преобразование для начинающих

В этой статье рассмотрены основные вопросы, касающиеся принципа действия АЦП различных типов. При этом некоторые важные теоретические выкладки, касающиеся математического описания аналого-цифрового преобразования остались за рамками статьи, но приведены ссылки, по которым заинтересованный читатель сможет найти более глубокое рассмотрение теоретических аспектов работы АЦП. Таким образом, статья касается в большей степени понимания общих принципов функционирования АЦП, чем теоретического анализа их работы.

В качестве отправной точки дадим определение аналого-цифровому преобразованию. Аналого-цифровое преобразование – это процесс преобразования входной физической величины в ее числовое представление. Аналого-цифровой преобразователь – устройство, выполняющее такое преобразование. Формально, входной величиной АЦП может быть любая физическая величина – напряжение, ток, сопротивление, емкость, частота следования импульсов, угол поворота вала и т.п. Однако, для определенности, в дальнейшем под АЦП мы будем понимать исключительно преобразователи напряжение-код.

Понятие аналого-цифрового преобразования тесно связано с понятием измерения. Под измерением понимается процесс сравнения измеряемой величины с некоторым эталоном, при аналого-цифровом преобразовании происходит сравнение входной величины с некоторой опорной величиной (как правило, с опорным напряжением). Таким образом, аналого-цифровое преобразование может рассматриваться как измерение значения входного сигнала, и к нему применимы все понятия метрологии, такие, как погрешности измерения.

Основные характеристики АЦП

АЦП имеет множество характеристик, из которых основными можно назвать частоту преобразования и разрядность. Частота преобразования обычно выражается в отсчетах в секунду (samples per second, SPS), разрядность – в битах. Современные АЦП могут иметь разрядность до 24 бит и скорость преобразования до единиц GSPS (конечно, не одновременно). Чем выше скорость и разрядность, тем труднее получить требуемые характеристики, тем дороже и сложнее преобразователь. Скорость преобразования и разрядность связаны друг с другом определенным образом, и мы можем повысить эффективную разрядность преобразования, пожертвовав скоростью.

Существует множество типов АЦП, однако в рамках данной статьи мы ограничимся рассмотрением только следующих типов:

Наибольшим быстродействием и самой низкой разрядностью обладают АЦП прямого (параллельного) преобразования. Например, АЦП параллельного преобразования TLC5540 фирмы Texas Instruments обладает быстродействием 40MSPS при разрядности всего 8 бит. АЦП данного типа могут иметь скорость преобразования до 1 GSPS. Здесь можно отметить, что еще большим быстродействием обладают конвейерные АЦП (pipelined ADC), однако они являются комбинацией нескольких АЦП с меньшим быстродействием и их рассмотрение выходит за рамки данной статьи.

Среднюю нишу в ряду разрядность-скорость занимают АЦП последовательного приближения. Типичными значениями является разрядность 12-18 бит при частоте преобразования 100KSPS-1MSPS.

Наибольшей точности достигают сигма-дельта АЦП, имеющие разрядность до 24 бит включительно и скорость от единиц SPS до единиц KSPS.

Еще одним типом АЦП, который находил применение в недавнем прошлом, является интегрирующий АЦП. Интегрирующие АЦП в настоящее время практически полностью вытеснены другими типами АЦП, но могут встретиться в старых измерительных приборах.

АЦП прямого преобразования

АЦП прямого преобразования получили широкое распространение в 1960-1970 годах, и стали производиться в виде интегральных схем в 1980-х. Они часто используются в составе «конвейерных» АЦП (в данной статье не рассматриваются), и имеют разрядность 6-8 бит при скорости до 1 GSPS.

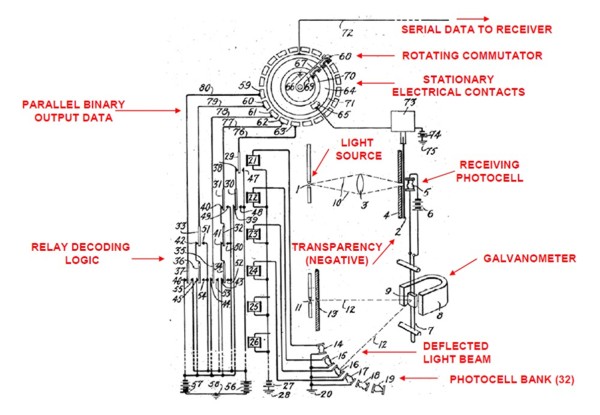

Архитектура АЦП прямого преобразования изображена на рис. 1

Рис. 1. Структурная схема АЦП прямого преобразования

Принцип действия АЦП предельно прост: входной сигнал поступает одновременно на все «плюсовые» входы компараторов, а на «минусовые» подается ряд напряжений, получаемых из опорного путем деления резисторами R. Для схемы на рис. 1 этот ряд будет таким: (1/16, 3/16, 5/16, 7/16, 9/16, 11/16, 13/16) Uref, где Uref – опорное напряжение АЦП.

Пусть на вход АЦП подается напряжение, равное 1/2 Uref. Тогда сработают первые 4 компаратора (если считать снизу), и на их выходах появятся логические единицы. Приоритетный шифратор (priority encoder) сформирует из «столбца» единиц двоичный код, который фиксируется выходным регистром.

Теперь становятся понятны достоинства и недостатки такого преобразователя. Все компараторы работают параллельно, время задержки схемы равно времени задержки в одном компараторе плюс время задержки в шифраторе. Компаратор и шифратор можно сделать очень быстрыми, в итоге вся схема имеет очень высокое быстродействие.

Но для получения N разрядов нужно 2^N компараторов (и сложность шифратора тоже растет как 2^N). Схема на рис. 1. содержит 8 компараторов и имеет 3 разряда, для получения 8 разрядов нужно уже 256 компараторов, для 10 разрядов – 1024 компаратора, для 24-битного АЦП их понадобилось бы свыше 16 млн. Однако таких высот техника еще не достигла.

АЦП последовательного приближения

АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий еще к Фибоначчи. В своей книге «Liber Abaci» (1202 г.) Фибоначчи рассмотрел «задачу о выборе наилучшей системы гирь», то есть о нахождении такого ряда весов гирь, который бы требовал для нахождения веса предмета минимального количества взвешиваний на рычажных весах. Решением этой задачи является «двоичный» набор гирь. Подробнее о задаче Фибоначчи можно прочитать, например, здесь: http://www.goldenmuseum.com/2015AMT_rus.html.

Аналого-цифровой преобразователь последовательного приближения (SAR, Successive Approximation Register) измеряет величину входного сигнала, осуществляя ряд последовательных «взвешиваний», то есть сравнений величины входного напряжения с рядом величин, генерируемых следующим образом:

1. на первом шаге на выходе встроенного цифро-аналогового преобразователя устанавливается величина, равная 1/2Uref (здесь и далее мы предполагаем, что сигнал находится в интервале (0 – Uref).

2. если сигнал больше этой величины, то он сравнивается с напряжением, лежащим посередине оставшегося интервала, т.е., в данном случае, 3/4Uref. Если сигнал меньше установленного уровня, то следующее сравнение будет производиться с меньшей половиной оставшегося интервала (т.е. с уровнем 1/4Uref).

3. Шаг 2 повторяется N раз. Таким образом, N сравнений («взвешиваний») порождает N бит результата.

Рис. 2. Структурная схема АЦП последовательного приближения.

Таким образом, АЦП последовательного приближения состоит из следующих узлов:

1. Компаратор. Он сравнивает входную величину и текущее значение «весового» напряжения (на рис. 2. обозначен треугольником).

2. Цифро-аналоговый преобразователь (Digital to Analog Converter, DAC). Он генерирует «весовое» значение напряжения на основе поступающего на вход цифрового кода.

3. Регистр последовательного приближения (Successive Approximation Register, SAR). Он осуществляет алгоритм последовательного приближения, генерируя текущее значение кода, подающегося на вход ЦАП. По его названию названа вся данная архитектура АЦП.

4. Схема выборки-хранения (Sample/Hold, S/H). Для работы данного АЦП принципиально важно, чтобы входное напряжение сохраняло неизменную величину в течение всего цикла преобразования. Однако «реальные» сигналы имеют свойство изменяться во времени. Схема выборки-хранения «запоминает» текущее значение аналогового сигнала, и сохраняет его неизменным на протяжении всего цикла работы устройства.

Достоинством устройства является относительно высокая скорость преобразования: время преобразования N-битного АЦП составляет N тактов. Точность преобразования ограничена точностью внутреннего ЦАП и может составлять 16-18 бит (сейчас стали появляться и 24-битные SAR ADC, например, AD7766 и AD7767).

И, наконец, самый интересный тип АЦП – сигма-дельта АЦП, иногда называемый в литературе АЦП с балансировкой заряда. Структурная схема сигма-дельта АЦП приведена на рис. 3.

Рис.3. Структурная схема сигма-дельта АЦП.

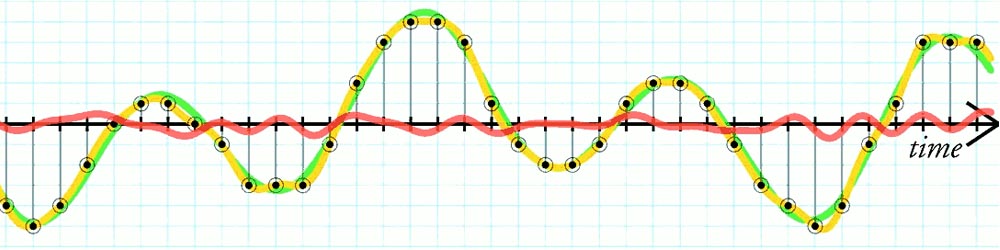

Принцип действия данного АЦП несколько более сложен, чем у других типов АЦП. Его суть в том, что входное напряжение сравнивается со значением напряжения, накопленным интегратором. На вход интегратора подаются импульсы положительной или отрицательной полярности, в зависимости от результата сравнения. Таким образом, данный АЦП представляет собой простую следящую систему: напряжение на выходе интегратора «отслеживает» входное напряжение (рис. 4). Результатом работы данной схемы является поток нулей и единиц на выходе компаратора, который затем пропускается через цифровой ФНЧ, в результате получается N-битный результат. ФНЧ на рис. 3. Объединен с «дециматором», устройством, снижающим частоту следования отсчетов путем их «прореживания».

Рис. 4. Сигма-дельта АЦП как следящая система

Ради строгости изложения, нужно сказать, что на рис. 3 изображена структурная схема сигма-дельта АЦП первого порядка. Сигма-дельта АЦП второго порядка имеет два интегратора и две петли обратной связи, но здесь рассматриваться не будет. Интересующиеся данной темой могут обратиться к [3].

На рис. 5 показаны сигналы в АЦП при нулевом уровне на входе (сверху) и при уровне Vref/2 (снизу).

Рис. 5. Сигналы в АЦП при разных уровнях сигнала на входе.

Более наглядно работу сигма-дельта АЦП демонстрирует небольшая программа, находящаяся тут: http://designtools.analog.com/dt/sdtutorial/sdtutorial.html.

Теперь, не углубляясь в сложный математический анализ, попробуем понять, почему сигма-дельта АЦП обладают очень низким уровнем собственных шумов.

Рассмотрим структурную схему сигма-дельта модулятора, изображенную на рис. 3, и представим ее в таком виде (рис. 6):

Рис. 6. Структурная схема сигма-дельта модулятора

Здесь компаратор представлен как сумматор, который суммирует непрерывный полезный сигнал и шум квантования.

Пусть интегратор имеет передаточную функцию 1/s. Тогда, представив полезный сигнал как X(s), выход сигма-дельта модулятора как Y(s), а шум квантования как E(s), получаем передаточную функцию АЦП:

То есть, фактически сигма-дельта модулятор является фильтром низких частот (1/(s+1)) для полезного сигнала, и фильтром высоких частот (s/(s+1)) для шума, причем оба фильтра имеют одинаковую частоту среза. Шум, сосредоточенный в высокочастотной области спектра, легко удаляется цифровым ФНЧ, который стоит после модулятора.

Рис. 7. Явление «вытеснения» шума в высокочастотную часть спектра

Однако следует понимать, что это чрезвычайно упрощенное объяснение явления вытеснения шума (noise shaping) в сигма-дельта АЦП.

Итак, основным достоинством сигма-дельта АЦП является высокая точность, обусловленная крайне низким уровнем собственного шума. Однако для достижения высокой точности нужно, чтобы частота среза цифрового фильтра была как можно ниже, во много раз меньше частоты работы сигма-дельта модулятора. Поэтому сигма-дельта АЦП имеют низкую скорость преобразования.

Они могут использоваться в аудиотехнике, однако основное применение находят в промышленной автоматике для преобразования сигналов датчиков, в измерительных приборах, и в других приложениях, где требуется высокая точность. но не требуется высокой скорости.

Самым старым упоминанием АЦП в истории является, вероятно, патент Paul M. Rainey, «Facsimile Telegraph System,» U.S. Patent 1,608,527, Filed July 20, 1921, Issued November 30, 1926. Изображенное в патенте устройство фактически является 5-битным АЦП прямого преобразования.

Рис. 8. Первый патент на АЦП

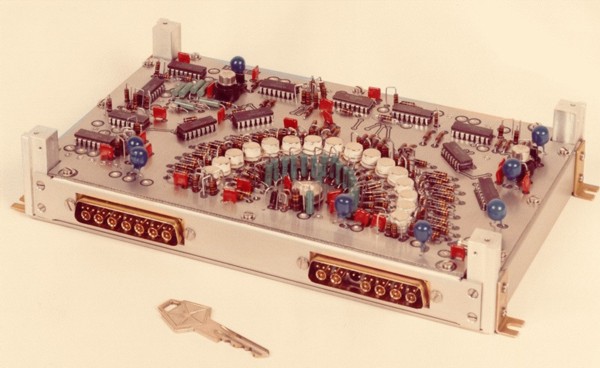

Рис. 9. АЦП прямого преобразования (1975 г.)

Устройство, изображенное на рисунке, представляет собой АЦП прямого преобразования MOD-4100 производства Computer Labs, 1975 года выпуска, собранный на основе дискретных компараторов. Компараторов 16 штук (они расположены полукругом, для того, чтобы уравнять задержку распространения сигнала до каждого компаратора), следовательно, АЦП имеет разрядность всего 4 бита. Скорость преобразования 100 MSPS, потребляемая мощность 14 ватт.

На следующем рисунке изображена продвинутая версия АЦП прямого преобразования.

Рис. 10. АЦП прямого преобразования (1970 г.)

Устройство VHS-630 1970 года выпуска, произведенное фирмой Computer Labs, содержало 64 компаратора, имело разрядность 6 бит, скорость 30MSPS и потребляло 100 ватт (версия 1975 года VHS-675 имела скорость 75 MSPS и потребление 130 ватт).

Для чего нужно опорное напряжение в ацп

В настоящее время имеется постоянно растущий спрос на прецизионные измерения, который наблюдается в самых разных отраслях индустрии — от аэрокосмической и оборонной промышленности и оборудования, используемого в нефтегазовой сфере, до производства фармацевтических и медицинских приборов. Калибровка и тестирование таких прецизионных измерительных систем ставят перед разработчиками и всей отраслью приборостроения задачи проектирования и производства контрольно-измерительного и испытательного оборудования, которое может достигать разрешения не менее 25 бит с точностью измерения не менее чем 7,5 разряда.

Публикуемая статья в виде авторского перевода [1] с рядом дополнений

рассматривает данную проблему и предлагает ее практические решения.

Введение

В фармацевтической промышленности используются высокоточные лабораторные весы, которым необходимо обеспечивать разрешение в 0,0001 мг в полномасштабном диапазоне 2,1 г, для чего и понадобится аналого-цифровой преобразователь (АЦП) с разрешением не менее 24 бит.

Для достижения столь высокого разрешения требуется цепочка сигналов с исключительно низким уровнем шума. На рис. 1 показана зависимость шума от таких параметров, как ENOB (Effective Number of Bits — эффективное число битов, служит для измерения качества аналого-цифрового преобразования), — это и является мерой динамического диапазона аналого-цифрового преобразователя, цифро-аналогового преобразователя или связанных с ними схем и отношения сигнал/шум (Signal-to-Noise Ratio, SNR). Здесь следует заметить, что SNR называется отношение среднеквадратического значения входного синусоидального сигнала к среднеквадратическому значению шума, который определяется как сумма всех остальных спектральных компонентов вплоть до половины частоты дискретизации, без учета постоянной составляющей (в идеале он равен шумам квантования, чего в реальной практике не бывает). Предельный уровень шума рассчитывается на основании источника опорного напряжения (ИОН) с напряжением VREF = 5 В и входного напряжения АЦП в режиме напряжения полной шкалы (Full Scale Range, FSR). Для обеспечения указанных требований, то есть для достижения 25‑битного разрешения или динамического диапазона, равного 152 дБ, максимально допустимый системный шум не должен превышать 0,2437 мкВ среднеквадратичного значения (далее — с.к.з.).

Опорное напряжение VREF устанавливает предел на уровень входного аналогового сигнала, который АЦП может обработать, то есть оцифровать. Уравнение (1) является функцией идеальной передачи АЦП, где выходной код в десятичной форме вычисляется по значениям VIN аналогового входного сигнала опорного напряжения VREF, а число битов АЦП задано как N:

Опорное напряжение VREF равно 5 В, получено от ИОН LTC6655-5.

Обратите внимание, что во всем диапазоне входного напряжения АЦП его уровень шумов остается постоянным при спектральной плотности шумового напряжения (далее — спектральная плотность шума), равной 35 нВ/√Гц, в то время как шумы источника входного сигнала АЦП хотя и возрастают до уровня 6 нВ/√Гц, но остаются низкими по сравнению с шумом ИОН, составляющим 96 нВ/√ Гц. Как показано на рис. 2, общий шум пропорционален входному напряжению постоянного тока АЦП. Это связано с тем, что с повышением VIN отношение VIN/VREF увеличивается, а потому, когда на вход АЦП подается максимально возможный для него уровень сигнала, шум опорного напряжения VREF доминирует над общим шумом системы. Индивидуальный шум каждого компонента в цепочке сигналов складывается в среднеквадратичном виде (то есть равен квадратному корню из суммы квадратов), что и дает в итоге форму графика, показанную на рис. 2.

Однако для достижения высокого разрешения измерения, равного 25 бит или более, даже некоторым лучшим из доступных на рынке интегральных источников опорного напряжения, имеющих низкий уровень шума, для его ослабления требуется помощь. Например, для получения желаемого динамического диапазона АЦП ослабить шум поможет добавление внешних схем, таких как внешние фильтры, или же использование специфических внутренних возможностей интегральных ИОН.

Далее показаны различные варианты реализации фильтров нижних частот (ФНЧ) и способы их применения для ослабления шумов источника опорного напряжения. Рассмотрены методы проектирования фильтров и присущие им компромиссы. Два типа фильтров нижних частот, которые будут обсуждаться в контексте темы ослабленного эталонного шума напряжения, — это простые пассивные RC-фильтры низких частот, а также активный ФНЧ на основе линейного графа сигналов (Signal Flow Graph, SFG). Результаты оценки системы с использованием SΔ-АЦП представлены в разделе, посвященном описанию характеристик конечного решения.

Подавление шумов с помощью пассивного фильтра нижних частот

На рис. 3 показана схема организации подачи опорного напряжения для АЦП, состоящая из стабилитрона, буферного усилителя и ФНЧ. Фильтр реализуется с помощью внешнего, как его называют, накопительного конденсатора С1, его эквивалентного последовательного сопротивления (Equivalent Series Resistance, ESR) и выходного импеданса операционного усилителя (ОУ). Частота среза такого пассивного RC-фильтра определяется как:

Большинство интегральных источников опорного напряжения разработано со сложным выходным каскадом, который способен играть роль драйвера для АЦП, требующего большую емкость на входе опорного напряжения. Например, выходной каскад ИОН серии LTC6655 спроектирован так, чтобы устойчиво функционировать при значении емкости конденсатора С1, равной 10 мкФ.

На рис. 6 в качестве примера приведена полная блок-схема ИОН LTC6655 исполнения LTC6655LN, далее мы рассмотрим его подробнее.

Как мы видим на рис. 5, когда емкость конденсатора на выходе выбрана минимальной, равной 2,7 мкФ, и максимальной, равной 100 мкФ, появляются пики шума. Эквивалентное последовательное сопротивление конденсатора на входе VREF АЦП уменьшает первый пик шума, но вводит второй пик на частоте 100 кГц и выше. Это можно объяснить тем, что на низких частотах влияние ESR мало, практически равно нулю, что приводит к улучшению запаса по фазе и уменьшению первого пика шума. Тем не менее этот ноль объединяется с собственным нулем LTC6655 и создает второй пик. Обратите внимание, что шумовой отклик, показанный на рис. 5, действителен только для опорного напряжения, сгенерированного микросхемой LTC6655.

Здесь хотелось бы попутно отметить, что, по опыту переводчика статьи, малошумящие стабилизаторы напряжения не настолько простые устройства в части шумов, как может показаться на первый взгляд. При определенных условиях, а именно при последовательно включенном по его входу резисторе, они превращаются в эффективные генераторы шума с широким спектром и довольно-таки высоким шумовым напряжением, достигающим сотни милливольт [8].

Впрочем, вернемся к нашей основной теме. Одним из альтернативных решений фильтрации опорного напряжения, позволяющего удалить пик шума и при этом правильно управлять АЦП, является добавление полнофункционального пассивного RC-фильтра нижних частот с последующим буфером. Устанавливая буфер, мы практически решаем проблему ограничений при реализации ФНЧ [11, 12] и получаем большую свободу при выборе конденсатора фильтра и конденсатора по входу опорного напряжения АЦП. Такое решение показано на рис. 7.

Однако увеличение сопротивления резистора R1 в ФНЧ хотя и может помочь достичь низкой частоты среза, но и способно привести к снижению точности преобразования АЦП, так как лишает источник опорного напряжения прецизионности.

При добавлении пассивного RC-фильтра разработчик обязательно должен учитывать его влияние на стабильность напряжения нагрузки и принимать во внимание отклик буферного усилителя поставщика VREF (необходимо учитывать влияние постоянной времени фильтра, то есть t = RC), поскольку это влияет на его переходные характеристики при управлении АЦП.

Для достижения требуемой переходной характеристики предлагается использовать буфер, как показано на рис. 7. Критические характеристики, которые следует учитывать при выборе кандидата на роль буферного усилителя, предусматривают сверхнизкие собственные шумы, способность работать на высокую емкость нагрузки, высокую скорость нарастания и высокий коэффициент усиления без отрицательной обратной связи (ООС), что подразумевает широкую полосу пропускания. В качестве буферных усилителей для передачи опорного напряжения на АЦП компания Analog Devices рекомендует использовать микросхемы операционных усилителей ADA4805-1 [9] и ADA4807-1 [10].

Подавление шумов источника опорного напряжения с использованием активного ФНЧ

В таблице 1 указаны необходимый динамический диапазон и требования по максимально допустимому уровню системных (то есть суммарных) шумов, который должен быть соблюден для достижения желаемого разрешения ENOB АЦП. Для расчета здесь использовались классические формулы: (3) для отношения сигнал/шум (SNR), где N — это число разрядов, и (4) для определения LSB (Least Significant Bit — младший значащий бит) наименьшего значения напряжения, которое может быть измерено АЦП:

В нашем случае необходим фильтр, АЧХ которого в полосе пропускания является плоской, то есть не имеет неравномерности ни в полосе пропускания, ни в полосе подавления. Именно такой фильтр будет поддерживать значение прецизионного напряжения постоянного тока с требуемой точностью. Из всех типов фильтров плоскую АЧХ в полосе пропускания и приемлемое затухание ФНЧ обеспечивает фильтр Баттерворта, который имеет и более линейную фазочастотную характеристику на частотах полосы пропускания, а значит, не будет давать недопустимую реакцию в виде выброса затухающего гармонического переходного процесса на импульсное воздействие.

Методика проектирования активных фильтров нижних частот

Для проектирования ФНЧ оптимален в данном случае метод на основе сигнально ориентированного графа (переходный граф сигналов, называемый еще «линейный переходный граф», или «линейный граф сигналов»; Signal-Flow Graph, SFG), который является графическим представлением системы, полученной из описывающей схему системы линейных уравнений [13]1.

Метод на основе SFG обеспечивает переход от передаточной функции фильтра к соответствующей топологии его схемной реализации. Эта теория может быть применена к проектированию аналоговых фильтров на основе активных схем. Главное преимущество подхода к проектированию фильтра с помощью SFG заключается в том, что коэффициент демпфирования, то есть добротность Q, и частоту среза можно задавать индивидуально. ФНЧ на основе SFG помогает ослабить шумы и, соответственно, улучшить SNR системы, но при этом имеет хорошие динамические характеристики, не генерируя артефакты при импульсном изменении тока (рис. 4). Но как компромисс это достигается за счет дополнительных затрат на необходимые компоненты, увеличения площади печатной платы и роста энергопотребления конечного решения.

Кроме того, ФНЧ на основе SFG может оказать влияние на выходное напряжение, которое, как мы помним, является опорным для АЦП. Эта погрешность связана с температурой, приводящей пусть и к небольшой ошибке, но все же снижающей точность преобразования. На рис. 10 показан пример перехода от передаточной функции к схемным блокам при проектировании фильтра нижних частот второго порядка методом SFG. С помощью уравнения (5) масштабирующий резистор R и конденсатор C устанавливают частоту среза фильтра:

Для получения более подробной информации о теории графов потоков сигналов можно обратиться к разделу «Управление обратной связью динамических систем», опубликованному в [13].

В этом разделе статьи были представлены основы проектирования, однако в текущей ситуации целесообразнее использовать, образно говоря, не логарифмическую линейку, а методы компьютерного моделирования. С этой целью компания Analog Devices предоставляет разработчикам два инструмента: универсальный инструмент для компьютерного моделирования LTspice (доступен для бесплатной загрузки по ссылке [15]), унаследованный после поглощения ею компании Linear Technology, и инструмент собственной разработки Analog Filter Wizard [16] (не утратившее актуальности краткое руководство по Analog Filter Wizard 2.0 доступно по ссылке [17]).

Возможности LTC6655LN

Учитывая все компромиссы решений в виде пассивного RC- фильтра низших частот с буфером и активного ФНЧ, синтезированного с использованием метода SFG, следует признать, что лучшим решением будет пассивный ФНЧ, интегрированный между источником опорного напряжения и его буферным усилителем. Это видно на рис. 11 на примере прецизионного источника опорного напряжения LTC6655LN [18], его полная блок-схема показана на рис. 6.

Представленная на рис. 11 реализация фильтра с использованием функциональных особенностей источника опорного напряжения LTC6655LN не только уменьшит площадь печатной платы, но и не будет создавать препятствия для сопряжения источника с АЦП. Применение буферного каскада с быстрым установлением, высоким входным импедансом и возможностью генерации втекающего и вытекающего тока поможет преодолеть проблемы, связанные с поведением нагрузки (имеется в виду динамическое изменение тока), сохранить точность опорного напряжения и улучшить характеристики переходного процесса.

Тестовая схема

Для сравнительной оценки производительности описанных в статье решений использовался прецизионный АЦП AD7177-2 [2] с источником опорного напряжения на LTC6655/LTC6655LN с шумоподавляющими конденсаторами емкостью 10 мкФ и LTC6655, за которым следовал активный фильтр ФНЧ, выполненный на основе SFG. Микросхема AD7177-2 представляет собой малошумящий 32‑разрядный SΔ-АЦП с быстродействием 10 kSPS, временем установления 100 мкс и буферами Rail-to-Rail. AD7177-2 интегрирован с программируемым цифровым фильтром нижних частот, который позволяет контролировать частоту обновления выходных данных в пределах 5 SPS – 10 kSPS.

Оценка производительности

На рис. 14 показана спектральная плотность шума, а на рис. 15 — частота обновления выходных данных в сравнении с ENOB, отражающая производительность АЦП AD7177-2 с его входом VREF, подключенным к LTC6655/LTC6655LN с шумоподавляющим конденсатором емкостью 10 мкФ или LTC6655 с фильтром, синтезированным на базе SFG. Получить представление о сравнении спектральной плотности шума на частоте 1 кГц можно из таблицы 4. Для сравнения на рис. 14, 15 показаны две важные области.

Втаблице 5 приведена сводная информация о характеристиках АЦП AD7177-2 с входом VREF, подключенным к LTC6655/LTC6655LN с шумоподавляющим конденсатором емкостью 10 мкФ или LTC6655 с SFG ФНЧ. Если входы АЦП связаны между собой, а вход VREF подключен к LTC6655,

то столбец шкалы для короткозамкнутого входа показывает наилучший динамический диапазон, которого может достичь АЦП AD7177-2 в конкретной реализации схемы подачи опорного напряжения. С входом на уровне почти максимального сигнала, то есть напряжения полной шкалы, АЦП LTC6655LN‑5 с шумоподавляющим конденсатором емкостью 10 мкФ, по сравнению

с LTC6655, в среднем на частоте обновления от 59,96 SPS увеличивает динамический диапазон измерения на 4 дБ. С другой стороны, LTC6655 с SFG ФНЧ при 59,96 SPS достигает в среднем приращения динамического диапазона, по сравнению с полученным для LTC6655LN‑5, на 7 дБ. Разница в динамическом диапазоне ниже 59,96 SPS меняется незначительно, а отклонение в основном связано с преобладанием низкочастотного фликкер-шума, генерируемого источником

напряжения постоянного тока на входе АЦП.

По сравнению с прямым подключением LTC6655LN использование конденсатора емкостью 10 мкФ, подключенного к выводу NR, уменьшает широкополосный шум на частоте 1 кГц на 62%, а решение LTC6655 с SFG ФНЧ сокращает широкополосный шум на 97%.

Заключение

При проектировании прецизионной системы аналого-цифрового преобразования с разрешением 25 бит или выше разработчики должны учитывать влияние шумов по входу источника опорного напряжения АЦП. Как показано на рис. 2, вклад шума источника опорного напряжения VREF в системный шум пропорционален использованию полномасштабного диапазона АЦП.

В этой статье показано, что добавление фильтра к прецизионному источнику опорного напряжения ослабляет шум по VREF, что приводит к снижению общего шума системы. Так, опорное напряжение, генерируемое LTC6655, с последующей фильтрацией активным ФНЧ, сформированным на базе SFG фильтра низких частот, по сравнению с LTC6655 без фильтра может уменьшить широкополосный шум на 97%. Однако это связано с дополнительными расходами на комплектующие, увеличением площади печатной платы, большим энергопотреблением и снижением точности измерения постоянного тока на несколько ppm.

Кроме того, опорное напряжение, полученное от такой схемы, может иметь зависимость от температуры. Учитывая компромиссы при использовании SFG ФНЧ, вариант в виде источника опорного напряжения выполнен на микросхеме LTC6655LN с шумоподавляющим конденсатором и обладает преимуществами в виде простой конструкции и малой потребляемой мощности. Это решение для снижения широкополосного шума требует только одного конденсатора и устраняет необходимость во внешнем буфере для управления АЦП. По сравнению с LTC6655 без фильтра источник опорного напряжения на LTC6655LN с конденсатором CNR емкостью 10 мкФ снижает широкополосный шум на 62%. Имея перед собой такое решение, в ряде случаев разработчики

вполне могут воспользоваться встроенным фильтром нижних частот LTC6655LN, чтобы

достичь желаемого разрешения своих конечных приложений.

Облегчить процесс проектирования можно, загрузив LTspice [15], а по ссылке [21] или по прямой ссылке из оригинала статьи [1] доступны файлы, необходимые для симуляции схемы, приведенной на рис. 8, схемы ФНЧ с SFG на рис. 12 и схемы источника напряжения постоянного тока с низким уровнем собственных шумов на рис. 13.